#### Master's Thesis

Czech Technical University in Prague

**F3**

Faculty of Electrical Engineering Department of Control Engineering

# Support for PREM on contemporary multicore COTS systems

Jan Doležal Open Informatics, Computer Engineering dolezj21@fel.cvut.cz

January 2019 Supervisor: Ing. Joel Matějka

## Acknowledgement

My gratitude for support during preparations of this work belongs to my supervisor Joel Matějka. I thank him especially for his guidance and also for his easy-going attitude that shifted the fun while creating this work to the completely different level. I am very grateful for the support provided by people from the CIIRC's Industrial Informatics Research Center. Namely I want to thank to Michal Sojka for all the valuable advices.

# / Declaration

I hereby declare that the submitted thesis is exclusively my own work and that I have listed all used information sources in accordance with the Methodological Guideline on Ethical Principles for College Final Work Preparation. In Prague, 8. 1. 2019

# Abstrakt

Práce přináší podporu pro vyvíjené výkonné aplikace reálného času, které pro svůj běh využívají vícejádrové běžně komerčně dostupné systémy.

Hlavním cílem práce je shrnout metody pro zvýšení předvídatelnosti doby běhu programu a provést testy nástrojů a hardware, které tyto metody využívají. Metody diskutované v této práci řeší problémy při konfliktech při přístupu ke sdíleným prostředkům na těchto platformách.

Konflikty při přístupech do hlavní paměti jsou řešeny za pomoci Predikovatelného výpočetního modelu (PREM). K vylepšení jeho spolehlivosti jsou zkoumány a vyhodnoceny možnosti omezení šířky pásma klientů paměti na úrovni pamětového kontroléru a také s využítím nástroje MemGuard na úrovní jader procesoru. Dvě ze zmíněných metod k omezení šířky pásma paměti jsou testovány na energeticky účinné vestavné platformě NVIDIA TX2.

Dále jsou prozkoumány efekty hardwarového dělení sdílených vyrovnávacích pamětí (Intel RDT) na platformě s procesorem řady Intel Xeon.

Výsledky ukázaly, že omezení šířky pásma na úrovni paměťového kontoléru není použitelné, protože není možné korektně separovat klienty. Naopak implementace MemGuardu byla úspěšně otestována na více testovacích případech. Testované hardwarové dělení sdílených vyrovnávacích pamětí zlepšuje předvídatelnost dle očekávání. Dále poskytujeme informace jak vyladit parametry nástrojů využívaných implementací PREM.

**Klíčová slova:** Systémy reálného času; WCET; Predikovatelný výpočetní model; omezování šířky pásma klientů paměti; Využití dělené skryté paměti.

**Překlad titulu:** Podpora PREM na současných multicore COTS systémech

# / Abstract

This work brings support for highperformance real-time applications that run on generic contemporary multicore systems referred to as Commercials Off-The-Shelf (COTS) platforms.

The main goal is to summarize the methods improving the predictability of program execution time and to test the tools and hardware utilizing these methods. Methods discussed in this work address issues of competition for shared resources in multicore COTS platforms.

Memory contention is resolved by PRedictable Execution Model (PREM) that schedules memory accesses in the To improve the reliability system. of PREM, we describe and employ bandwidth limiting capabilities to the memory clients. We evaluate throttling of memory controller clients and the MemGuard tool, which allows throttling of CPU cores, and profile the implementation to show its overhead. Tests are performed to see the effects of throttling on the memory controller The two presented methods level. to throttle bandwidth of the memory clients are tested on the low-power embedded platform NVIDIA TX2.

Further, we address shared cache contention using methods for partitioning shared cache (Intel RDT, Page Color). We showed the effects of the hardware partitioning using RDT on an Intel Xeon series processor.

The results have shown that throttling of the memory controller is not usable since we cannot separate particular clients properly. Further, MemGuard was successfully tested on multiple use cases. Tested hardware cache partitioning improves the system performance as expected. Moreover, we provide details about the fine-tuning of the tools used by PREM.

**Keywords:** Real-time systems; Worst-Case Execution Time; Predictable Execution Model; throttling memory clients bandwidth; Partitioned Cache Utilization.

v

# Contents

|             | troduction                                                                 |            |

|-------------|----------------------------------------------------------------------------|------------|

| 2 Ba        | ackground                                                                  | .3         |

| 2.1         | Real-time embedded systems                                                 | .3         |

|             | 2.1.1 Worst-case execution                                                 |            |

|             | time (WCET) $\dots$                                                        | .4         |

|             | 2.1.2 WCET and contempo-                                                   |            |

|             | rary hardware                                                              | 4          |

|             | 2.1.3 Timing constraints in                                                |            |

|             | industry                                                                   | .5         |

| 2.2         | Multicore systems and real-                                                |            |

|             | time applications                                                          | .5         |

| 2.3         | Methods increasing pre-                                                    |            |

|             | dictability of execution time                                              |            |

|             | within multicore system                                                    | .5         |

| 2.4         | Memory hierarchy                                                           | .6         |

|             | 2.4.1 Data request propaga-                                                |            |

|             | tion                                                                       | 7          |

|             | 2.4.2 Cache organization                                                   | 8          |

|             | 2.4.3 Writing data back to                                                 |            |

|             | main memory                                                                |            |

|             | 2.4.4 Cache inclusion policy $\dots$                                       |            |

|             | 2.4.5 Cache coherency                                                      | 10         |

|             | 2.4.6 Caches incorporated in                                               |            |

|             | virtual address model                                                      | 10         |

|             | 2.4.7 Caches in contempo-                                                  |            |

|             | rary hardware                                                              | 12         |

|             | 2.4.8 Quality of service in                                                |            |

|             | relation to cache                                                          | 12         |

| 2.5         | Performance Monitor Unit                                                   |            |

|             | (PMU)                                                                      |            |

| 2.6         | Hypervisor                                                                 |            |

|             | 2.6.1 Hardware partitioning                                                | 15         |

| 2.7         | PRedictable Execution Mod-                                                 |            |

|             | el (PREM)                                                                  |            |

|             | 2.7.1 WCET-aware compiler                                                  | 17         |

|             | 2.7.2 Decoupled Access Exe-                                                | 1.0        |

| 0.0         | cute (DAE)                                                                 | 18         |

| 2.8         | MemGuard: limiting memo-                                                   | 10         |

| 0.0         | ry bandwidth of CPU cores                                                  | 18         |

| 2.9         | 8                                                                          |            |

|             | solution addressing cache                                                  | 20         |

| 2 14        | contention                                                                 |            |

|             | ethodology<br>NVIDIA Tegra X2                                              |            |

| <b>Э</b> .1 |                                                                            |            |

|             | <ul><li>3.1.1 System organization</li><li>3.1.2 Memory subsystem</li></ul> |            |

|             | J.1.∠ Memory subsystem                                                     | ∠ <b>J</b> |

| 3.1.3 Throttling memory                                |          |

|--------------------------------------------------------|----------|

| controller clients                                     | 25       |

| 3.1.4 Processing units                                 | 26       |

| 3.1.5 Performance Monitor                              |          |

| Unit (PMU)                                             | 27       |

| 3.2 Intel Xeon W                                       | 28       |

| 3.2.1 Memory controller                                | 28       |

| 3.2.2 Cache organization                               | 28       |

| 3.2.3 Resource Director                                |          |

| Technology (RDT)                                       | 28       |

| 3.2.4 Performance Monitor                              |          |

| Unit (PMU)                                             | 30       |

| 3.3 Measuring performance                              |          |

| events under Linux                                     | 30       |

| 3.4 Jailhouse: HV partitions HW .                      | 31       |

| 3.4.1 Setup                                            | 33       |

| 3.5 Benchmarks                                         | 33       |

| 3.6 Design of experiments                              | 34       |

| 3.6.1 Throttling memory                                |          |

| clients                                                | 34       |

| 3.6.2 Profiling MemGuard                               |          |

| implementation                                         | 35       |

| 3.6.3 Hardware cache parti-                            |          |

| tioning                                                |          |

| 4 Evaluation                                           |          |

| 4.1 Throttling memory clients                          |          |

| 4.1.1 Measurement results                              | 39       |

| 4.2 Profiling MemGuard imple-                          |          |

| mentation                                              | 41       |

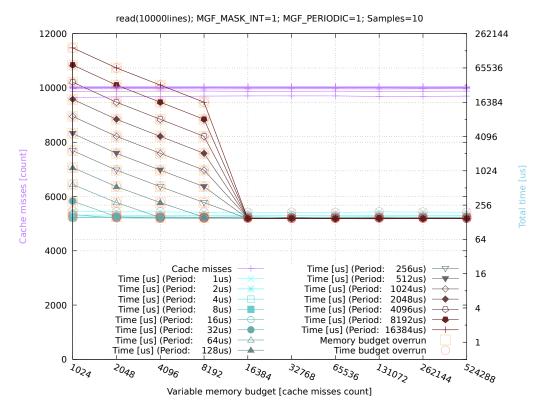

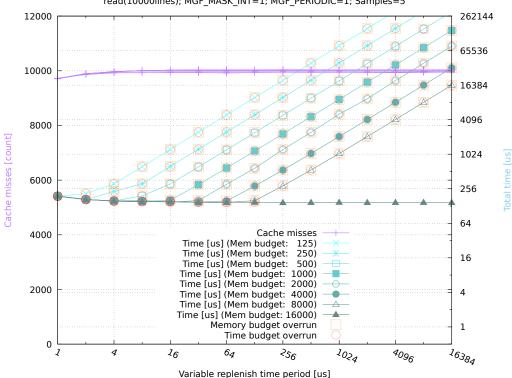

| 4.2.1 Profiling basic MG pa-                           |          |

| rameters                                               | 41       |

| 4.2.2 Reliability of Mem-                              |          |

| Guard                                                  |          |

| 4.2.3 MemGuard as a profiler.                          | 45       |

| 4.2.4 MemGuard upon                                    |          |

| real-world application:                                | 10       |

| KCF tracker                                            |          |

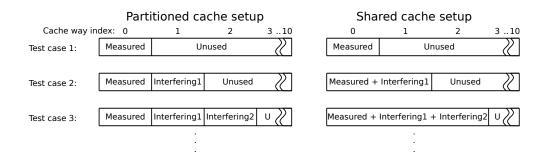

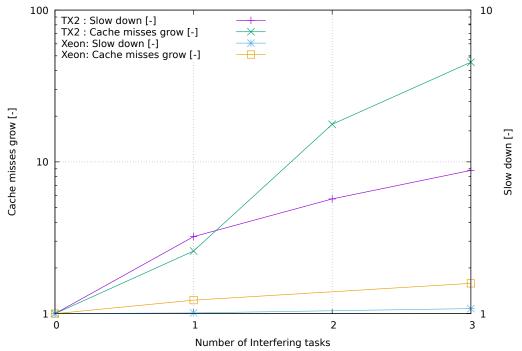

| 4.3 Hardware cache partitioning                        | 48       |

| 5 Conclusion                                           | 51<br>50 |

| References                                             |          |

| A Specification                                        |          |

| A.1 Specification in English<br><b>B Abbreviations</b> |          |

| D ADDreviations                                        | 98       |

# Tables / Figures

| 2.1. | MOESI cache coherency pro-   |

|------|------------------------------|

|      | tocol states 10              |

| 2.2. | Cache parameters of contem-  |

|      | porary hardware platforms 14 |

| 3.1. | Parameters of the Tegra X2   |

|      | system on module 22          |

| 3.2. | Registers used to throttle   |

|      | groups of clients            |

| 3.3. | Cache parameters of TX2      |

|      | CPU clusters 27              |

| 3.4. | Xeon W-2133 cache parame-    |

|      | ters                         |

| 3.5. | RDT support on Xeon pro-     |

|      | cessor versions 29           |

| 3.6. | Intel PMU: selected perfor-  |

|      | mance events 30              |

| 3.7. | Complexity of the used Poly- |

|      | Bench benchmarks 33          |

| 4.1. | Percentage overhead of the   |

|      | MemGuard for various re-     |

|      | plenish time periods 45      |

| 2.1.  | Execution time distribution4                          | 4 |

|-------|-------------------------------------------------------|---|

| 2.2.  | CPU vs. DRAM perfor-                                  |   |

|       | mance in time                                         | 7 |

| 2.3.  | Multi-level cache                                     | 3 |

| 2.4.  | Parts of memory address                               |   |

|       | driving cache element choice9                         | 9 |

| 2.5.  | x86 arch: paging with 4kB                             |   |

|       | long pages 12                                         | 2 |

| 2.6.  | *                                                     |   |

|       | Lookaside Buffer and Page                             |   |

|       | Table miss   13                                       |   |

|       | Hypervisor types comparison 15                        | 5 |

| 2.8.  | Comparison of virtualization                          |   |

| • •   | types                                                 | ö |

| 2.9.  |                                                       | _ |

| 0.10  | constant execution time 17                            | 7 |

| 2.10. | Compiler outline with sup-                            | ~ |

| 0.11  | port for multiple targets 18                          | 5 |

| 2.11. | 0                                                     | 0 |

| 0 10  | ture                                                  | J |

| 2.12. | 0                                                     | n |

| 2.13. | tive example                                          | J |

| 2.13. | 1 1 0 0                                               | 1 |

| 3.1.  | used to partition cache 21<br>TX2: Block diagram of a | L |

| J.1.  | Parker series processor 23                            | 2 |

| 3 2   | TX1: Memory Controller:                               | J |

| J.2.  | Path between DRAM mod-                                |   |

|       | ules and MC clients 2 <sup>4</sup>                    | 1 |

| 3.3.  |                                                       | T |

| 5.5.  | Arbitration among MC clients . 25                     | 5 |

| 3.4.  | _                                                     | , |

| ••••  | Technology                                            | 9 |

| 3.5.  | Jailhouse: hardware static                            |   |

|       | partitioning                                          | 2 |

| 3.6.  |                                                       |   |

|       | phases                                                | 2 |

| 3.7.  | KCF tracker illustration 36                           | 6 |

| 3.8.  | Cache partitioning experi-                            |   |

|       | ment 36                                               | ô |

| 4.1.  | TX2 vs. Xeon W: cache re-                             |   |

|       | lated relative comparison of                          |   |

|       | performance 38                                        | 3 |

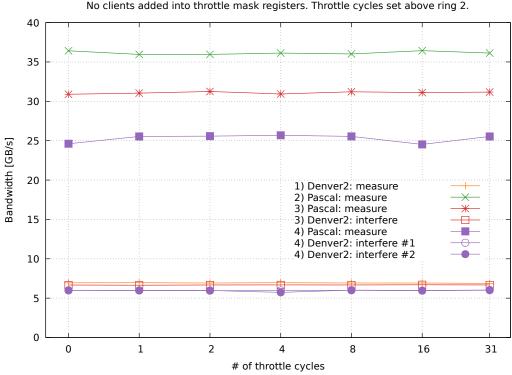

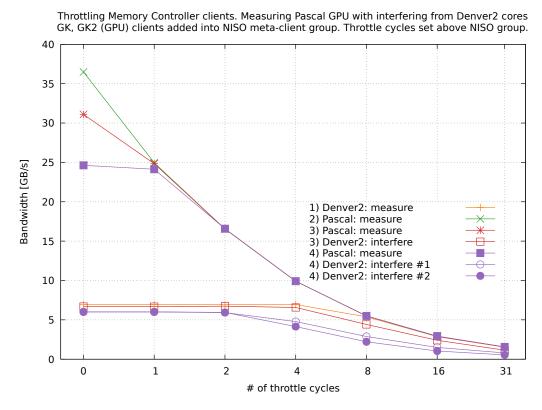

| 4.2.  | TX2: Throttle MC Clients:                             |   |

|       | Throttle on ring 2. No clients                        |   |

|       | added 39                                              | 9 |

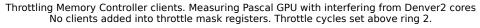

| 4.3.  | TX2: Throttle MC Clients:                               |

|-------|---------------------------------------------------------|

|       | Throttle on ring 0. No clients                          |

|       | added 40                                                |

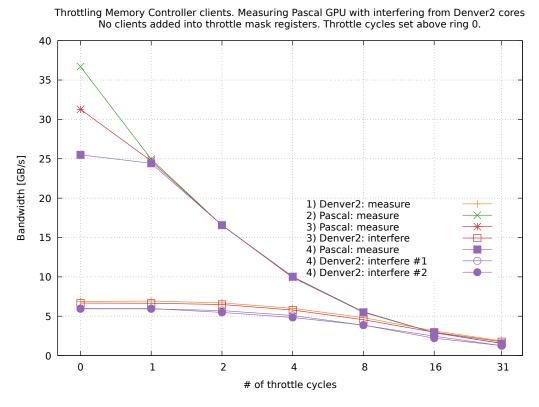

| 4.4.  | TX2: Throttle MC Clients:                               |

|       | Throttle on NISO group. No                              |

|       | clients added 40                                        |

| 4.5.  | TX2: Throttle MC Clients:                               |

|       | Throttle GPU within NISO                                |

|       | group                                                   |

| 4.6.  |                                                         |

|       | plication's performance re-                             |

|       | sponse with varying MG pa-                              |

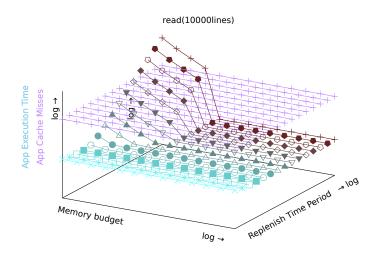

| 47    | rameters                                                |

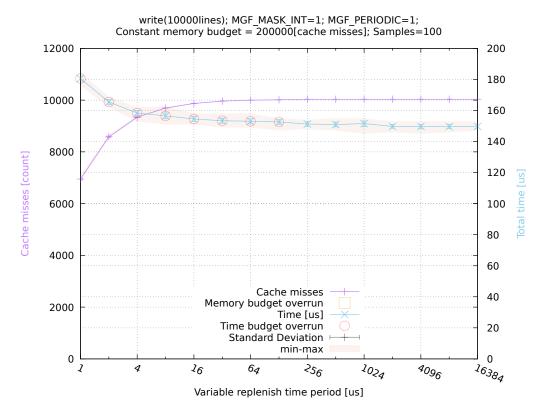

| 4.1.  | ry budget behavior 43                                   |

| 4.8.  |                                                         |

| 4.0.  | ish time period behavior 43                             |

| 4.9.  | MemGuard: profiling timer                               |

|       | ISR overhead 44                                         |

| 4.10. | MemGuard: scatter plot of                               |

|       | million measurements that                               |

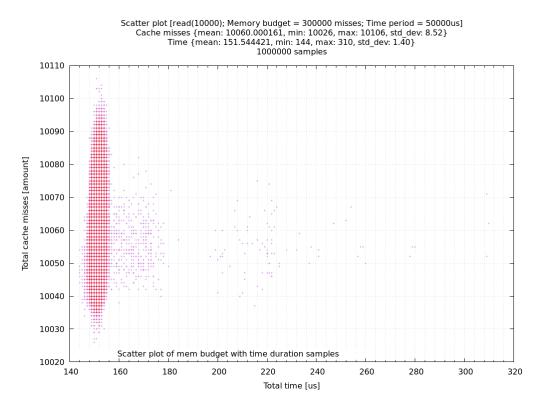

|       | involve task reading ten                                |

|       | thousand cache lines 45                                 |

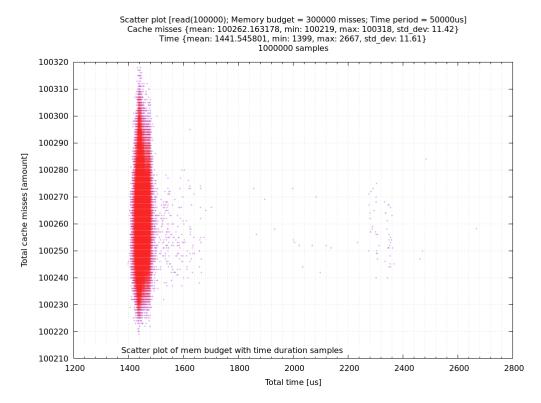

| 4.11. | MemGuard: scatter plot of                               |

|       | million measurements that                               |

|       | involve task reading hundred                            |

|       | thousand cache lines                                    |

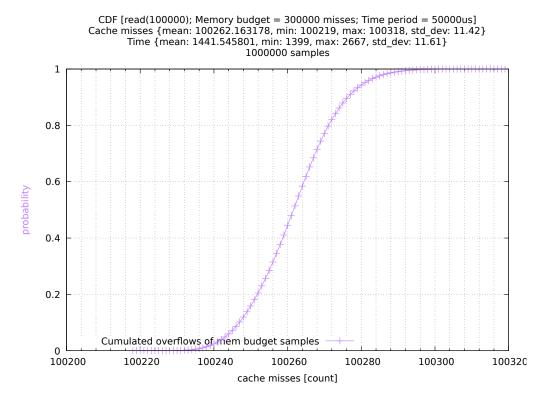

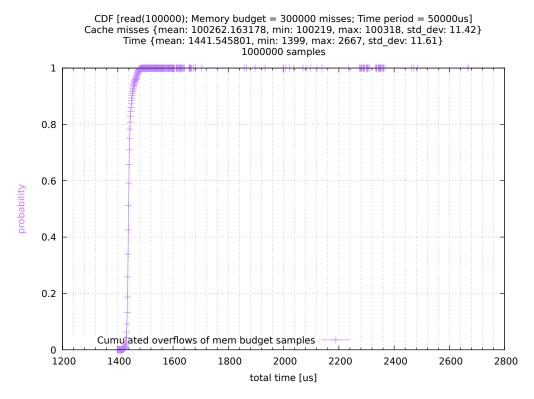

| 4.12. | MemGuard: CDF: cache                                    |

|       | misses plot of million mea-                             |

|       | surements that involve task<br>reading hundred thousand |

|       | cache lines 47                                          |

| 4 1 3 | MemGuard: CDF: execution                                |

| 4.13. | time plot of million measure-                           |

|       | ments that involve task read-                           |

|       | ing hundred thousand cache                              |

|       | lines 47                                                |

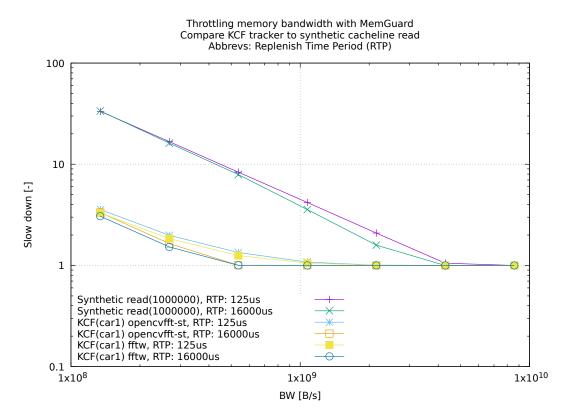

| 4.14. | MemGuard: compare real-                                 |

|       | world and synthetic applica-                            |

|       | tions 48                                                |

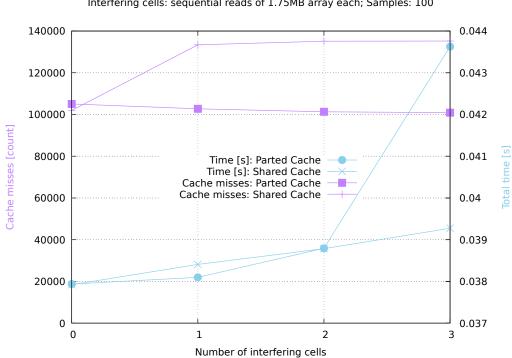

| 4.15. | Shared vs. partitioned cache:                           |

|       | cache misses and times aver-                            |

|       | ages 49                                                 |

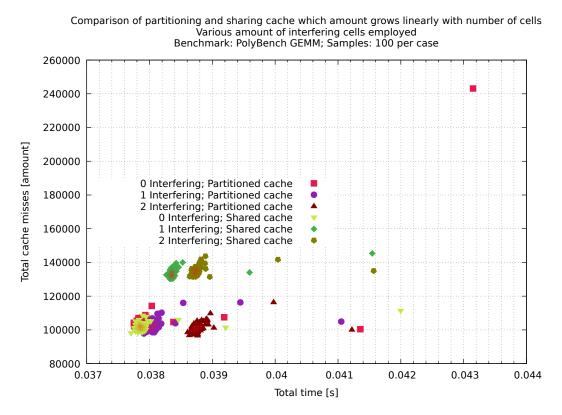

| 4.16. | Shared vs. partitioned cache:                           |

|       | scatter plot 50                                         |

# Chapter **1** Introduction

The requirements of real-time embedded systems on their computational power increase as they are expected to solve the new feature-rich challenges with higher and higher complexity. There are ongoing efforts to simplify everyday life tasks. The example of such effort is research in the area of autonomous transportation. To cover the market, the devices that carry out such tasks need to be distributed in high numbers. Therefore, the price of the underlying devices used in such solutions becomes increasingly important. The custom hardware designed for any particular real-time application cannot provide the low price, so the attention shifted to the use of generic multi-core computation platforms referred to as Commercials of The Shelf (COTS).

COTS platforms bring high performance and low price. However, their properties are not optimized for critical real-time applications. Programs driving critical realtime systems have to provide their result within the specified deadline. Otherwise, an event threatening human life or property may occur. Real-time systems and their parts are therefore subjected to the worst-case execution time (WCET) analyses to be sure no deadline within the system is exceeded. The hardware of the multicore COTS platforms is targeting primarily non-real-time segments, and it is optimized for high average performance (i.e., low average execution time) by utilizing complex superscalar CPUs and multi-level caches. Sparse random occurrences of the significantly lower performance are not considered to be an issue. Therefore, use of such systems in realtime applications lead to pessimistic estimations of worst-case execution times, and significant underutilization of the designed system.

In multicore COTS platforms the possibility of the state that leads to the occurrence of unusually high execution time is caused by shared resources. Shared resources are contention points such as shared last level cache and shared main memory bus. Competition of parallelly running CPU cores for these shared resources can introduce significant timing delays and increase execution times of all contenders.

The focus of this work is on a research of the methods to decrease WCET by increasing the predictability of program execution time, and on evaluating some of these methods using the COTS platforms. The effort of these methods is to moderate quality of service provided by shared resources so that it corresponds to the system's requirements.

PRedictable Execution Model is a mechanism addressing competition for shared main memory. PREM coschedules all active components (e.g., CPU cores, I/O peripherals) in the system. Each component has a time slot in a static schedule where it can access the memory. The scheduler notifies components about beginning and end of their memory phase. If the task executed by certain component is aware of PREM, it is called predictable task. If not, it is called legacy task. The predictable task is prepared in a way it contains memory phases and executes phases that are in line with the static schedule. In memory phase the, data necessary for the execute phase are loaded to the component-local memory (cache for CPU). During execute phase the component performs no memory accesses leaving the memory bus free to be used by other components. It is not possible to premize every task because many of them have complex memory access patterns. Such legacy tasks could unpredictably interfere with the memory phases of predictable tasks.

The memory phase of predictable task suffering from negative interference might not be completed by the static schedule and expected execution time of such task could be crossed. This could lead to serious consequences if the task employed was a real-time task. Moreover, this could start chain reaction breaking down the static schedule and crashing the whole system in the end.

To ensure that memory phase finishes within its deadline, a certain level of the bus bandwidth has to be guaranteed for the usage by the statically scheduled memory phases. Such a guarantee is provided when the bandwidth of all legacy components is limited. This way the memory bus bandwidth is partitioned among predictable and legacy components. This motivated the exploration of methods to limit the bandwidth of legacy tasks.

There exist methods to partition shared cache among contenders leading to improved predictability of their execution time.

This work addresses the following methods or employes the following tools:

- PRedictable Execution Model (PREM) that addresses competition for main memory

- MemGuard which is the tool to limit memory bandwidth of the CPU cores utilizing Performance Monitor Counters

- memory controller as the mean to limit memory bandwidth of its clients

- cache partitioning as a method addressing contention for the space in a cache shared among CPU cores

- in software with page coloring

- in hardware with Intel Resource Director Technology

- Jailhouse hardware partitioning hypervisor

- version with the implemented MemGuard support

- version with the support for RDT

There are hardware and software solutions that we tested. Two tested software solutions are related to the throttling bandwidth of memory clients. First, we test throttling on the memory controller level. Next, the MemGuard tool is profiled. Both aforementioned solutions are evaluated using low-power embedded platform NVIDIA Tegra X2. Lastly, we tested the behavior of the hardware cache partitioning with RDT. This feature is available on some of the Intel Xeon processors.

Memory controller and its throttling mechanism are complex devices with hierarchical organizations. Moreover, NVIDIA does not provide a complete description of the controller in its manuals. The setup of test incorporating memory controller is, therefore, challenging task.

The work partly originated as a contribution to the European project HERCULES  $^{1)}$ .

<sup>1)</sup> https://hercules2020.eu/

In section 2.1 are stated main objectives of embedded systems and real-time systems along with their analysis. Section 2.2 briefly introduces multicore systems and problems of their usage in the area of real-time applications. The methods increasing predictability within multicore systems were briefly introduced in the section 2.3. In section 2.4 the chapter continues with the memory hierarchy description, highlighting especially caching mechanism. The memory hierarchy is followed by the section 2.5 that describes Performance Monitor Unit allowing to profile, among others, characteristics of the memory subsystem. The section 2.6 talks about hardware partitioning with the utilization of hypervisor. Next follows the section 2.7 describing PRedictable Execution Model. Section 2.8 describes MemGuard – tool to reservate memory bandwidth for execution unit. Finally there is an example of software based cache partitioning in section 2.9.

## 2.1 Real-time embedded systems

In our daily lives, people use computer systems that have dedicated purpose and that are controlling some larger system. These are called embedded systems. Several examples follow: ticket vending machine, cash register, digital watch, mobile phone, microwave oven, washing machine, medical imaging, GPS navigation, anti-lock braking system or infotainment system.

There are several highly important objectives for current embedded systems [1]:

- low development costs

- short time-to-market

- dependability

- temperature efficiency

- energy efficiency

- average-case performance

- worst-case performance

To ensure safety, the devices are required to response to an event within the certain time constraint. System having this property is referred to as a real-time system. My favorite example is the airbag responding to a collision. If the system responses to the collision too late, the airbag inflation might not help and it could even cause additional injuries to the passenger. This example shows hard real-time system. That is a system where missing the time constraint (so called deadline) can lead to damage of property or loss of lives.

There exist also soft real-time systems. If the deadline is missed in these systems, the result of computation invoked by the event can still be utilized, but the usefulness of such a result degrades as the time advances further beyond the deadline. Very frequent example of soft real-time systems are live audio-video systems, where late data delivery/processing leads to degraded quality of the output. [2]

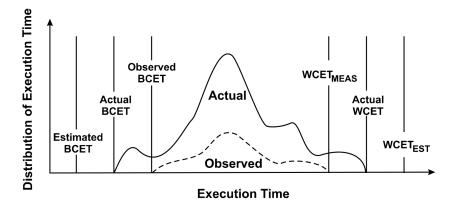

Figure 2.1. Execution time distribution. Best/Worst-Case Execution Times. [1]

#### **2.1.1** Worst-case execution time (WCET)

To ensure that the time constraint is fulfilled whenever the code is invoked, there is need to know the longest possible time interval during which the given code can run from its invocation. Such a period is referred to as worst-case execution time (WCET).

To find the maximum execution time it is not feasible to exhaustively explore all the possible execution times since software for contemporary architectures exhibit a too large state space [1]. Thus measured WCET, WCET<sub>MEAS</sub>, is not sufficient parameter for the verification of hard real-time systems. However, it can be utilized for more relaxed real-time systems, where there is added a safety margin to WCET<sub>MEAS</sub>.

The more scientific approach includes usage of formal methods to reason about WCET. With this approach, the code is analyzed statically to determine properties of its temporal behavior [1]. Nevertheless WCET cannot be derived from every program due to undecidability. Analyzed programs must meet constraints such as guaranteed termination, bounded recursion depths and loop iteration counts.

#### 2.1.2 WCET and contemporary hardware

Since embedded systems are getting more and more complex, there is a need to use highperformance commercials off the shelf (COTS) hardware [3]. There is need to account for architectural features of such hardware. Common architectural features such as superscalar pipelines and caches are targeting reduction of average-case execution time (ACET). It is however not possible to precisely analyze these features using static methods [1].

Furthermore, a sound approximation of the actual WCET demands an abstraction of possible inputs and initial states of the system, which introduces another source of imprecision [1]. As a consequence, the determination of the actual WCET has to be relaxed to the derivation of an upper bound on the execution time of the task. These bounds represent the estimated WCET<sub>EST</sub>. The process of estimating the WCET is called timing analysis. [1]

The relation among mentioned worst-case execution times is as follows

$$WCET_{MEAS} < WCET_{Actual} < WCET_{EST}$$

. Example that helps to understand the execution time distribution is in the figure 2.1. To ensure safeness,  $WCET_{Actual} \leq WCET_{EST}$  must hold. The estimated WCET gets more precise when  $WCET_{EST} - WCET_{Actual} \rightarrow 0$ . This is referred to as tightness.

#### 2.1.3 Timing constraints in industry

The availability of timing-aware software development tools is insufficient. As a result trial-and-error approach is often used in practice. The software is tuned until  $WCET_{MEAS} + Safety \ margin$  is less than timing constraints. [1] If the optimizations of WCET create enough time reserve before the deadline either cheaper hardware may be utilized, or the software may be modified to do more work.

## 2.2 Multicore systems and real-time applications

Historically the performance of silicon system increased with usage of higher clock frequencies. Higher frequency allows more operations to be performed within the same time. With higher frequency there is produced more heat and if the frequency is increased too much, the limit may be reached, where too much heat can damage the system.

Since the performance couldn't be increased by scaling frequency anymore, another way to increase performance came to broad use. There are used multiple computational cores i.e., multiple CPUs in one system.

Within real-time domain, one of the main issues with multicore systems is the main memory shared among the cores. When multiple cores share the main memory it leads to contention over access to the memory. In turn this increases the timing unpredictability. Existing WCET analyses are extremely pessimistic for these configurations. Since industry relies on those analyses, the usage of multi-core systems in these areas is limited unless new approaches are utilized. [4]

In this work the approach to address memory contention described in previous paragraph is PRedictable Execution Model (PREM). Further details on PREM can be found in section 2.7.

Memory organization is thoroughly described in section 2.4.

# 2.3 Methods increasing predictability of execution time within multicore system

In the area of our interest – real-time embedded systems – there is an aim to utilize simple ideas so the whole system is deeply understood. This way people can more easily reason about the guarantees within the system and potentially provide certified system.

With PRedictable Execution Model (PREM) basically the main memory accesses are scheduled among the clients of the memory. This way the timing of memory accesses is more predictable and theoretical WCET bloated by possible clashes of concurrent accesses to the memory can be decreased. PREM is described in detail in the section 2.7.

With PREM each task is divided into memory phases to retrieve some data and computation phases to work on those data. In memory phase the data are prefetched to the local memory of an execution unit. Tasks that may be divided into these phases are called predictable intervals. PREM employs static scheduling of intervals. To achieve predictability it is necessary to shedule the memory phases so that they follow up each other. This is easily done utilizing static scheduling. In practice this means that there is one unit accessing memory and all other execution units are either in their compute phase or stalled. This way WCET in execution phases can be decreased, since each data access is faster. Not all tasks may be easily separated into memory and computation phase due to its complexity. These undividable tasks are called compatible or legacy intervals. A compatible interval may seriously interfere with predictable interval when they run concurrently. To regulate the level of interference there is required certain level of memory bandwidth for the predictable intervals. This allows to guarantee WCET.

In this paragraph there are presented methods to limit the bandwidth of the computation unit. Some platforms utilize memory controllers that have its clients attached in a way their bandwidth can be limited directly. For example when the GPU, as the computation unit, is one of the MC's clients, its memory accesses can be limited on the MC level to ensure it does not interfere with CPU. The CPU could be approached if only each CPU core was a client to the memory controller. However the whole CPU cluster is typically attached as one MC client. To limit memory bandwidth of certain CPU core there may be utilized Performance Monitor Unit (PMU). The PMU captures various statistics related to the performance of CPU. It may also essentially count memory accesses. The memory bandwidth can be limited in the following way. In the given period of time certain amount of the memory accesses is allowed to be executed. The execution of the core that exceeded the limit is suspended until the period times out. The method using Performance Measuring Counters was introduced by MemGuard [5].

Any task requires certain resources i.e., hardware to achieve its goal. This includes certain portion of memory, execution unit and it may require further devices such as timers, DMAs and many others. Hardware often needs to be shared among tasks as the number of its instance is limited. In general however, sharing resources may lead to timing unpredictabilities originating in the manager of such shares.

Consider the hardware is partitioned to certain bundles. Above each bundle there runs specific task. With such organization the simple model is obtained. It is possible to reason about such model more easily and easily ensure the bundles mutual negative interference is mitigated. An example follows: the reserved resources for certain task could include few regions in the physical memory address space, CPU cores 4 & 5 and memory mapped PCI device. No other task would get access to the resources mentioned in the previous sentence. More on this in section 3.4.

CPU clusters have typically some very fast per core memory as well as fast per cluster memory. These memories are meant to capture part of the data backed by main memory and provide execution unit that reaches for the same data repeatedly with fast accesses to such data. Described on-chip memories are called caches and they are hidden from direct access by the programmer. Since per cluster memory is shared among cores it may occure that one core thrashes data of the other core in such a cache. This behavior is undesirable since it is source of unpredictability. Hence some manufacturers equipped the shared caches with the ability to be partitioned. When partitioned, certain part of cache belongs exclusively to certain cores. Besides the trend of manufacturing processors with this effective cache management [6] there also exists software method to partition the cache called Page Coloring [7].

### 2.4 Memory hierarchy

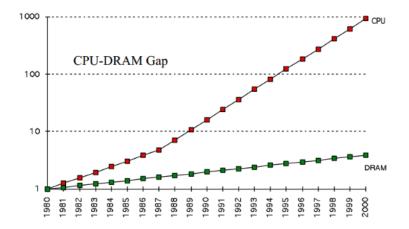

Nowadays, computer systems utilize fast processors with high frequencies and fairly slower main memories. Figure 2.2 compares the evolution in speeds of processor and main memory at the end of last century. When the processor executes code, it first needs to load the executed code itself and then to load the data that are referenced by the code. Between main memory and processor there are present devices called caches.

Cache is much faster memory compared to the main memory. If the caches were not present in the system, it would take hundreds of processor cycles for the main memory to load a data item. That would lead to the most of the processor time to be wasted.

Cache is basically small piece of memory but much faster than the main memory. Different technology is used for the main memory (Dynamic RAM: capacitor), and for caches (Static RAM: flip-flop). The price is the main reason why the main memory is not made with the same fast technology as the one used in caches. Another reason is the space requirements for SRAM technology. Besides the fact that for storing one bit DRAM requires only one transistor along with a capacitor whereas SRAM requires as much as six transistors, the wire capacities charge faster with larger transistors. Therefore the speed depends on the time needed to charge these wire capacities, and the speed and space on the die required have the inverse relationship. I.e., having two caches of the same byte capacity the one taking up more space on the die (larger transistors) is faster. Further, the high amount of memory requires more complex controllers and typically when the complexity rises the speed goes down.

When writing code, programmer ponders over virtual memory model, and in general, he does not interact with caches directly. Detailed information can be found in a serial about memory at the Linux Weekly News [8].

Figure 2.2. Processor and memory performance comparison throughout the years.

#### 2.4.1 Data request propagation

In memory hierarchy, there is typically more than one cache level where the cache level closer to the CPU is smaller and faster than the level farther from the CPU. Smaller cache has simpler control circuits hence it is faster (relates to the propagation times).

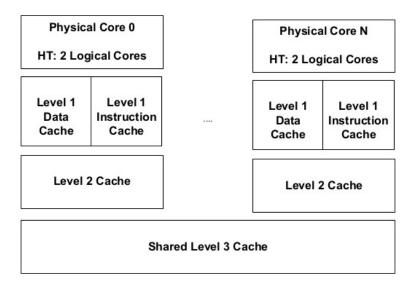

When CPU accesses the data item, it starts by searching the item in the first level cache. Cache either returns an item, in case of the cache hit, or informs the CPU about cache miss, in case the item is not present in the cache. In the event of a miss, CPU tries to find the data item in the next cache level. Eventually, if the item is not found in any cache level it is retrieved from the main memory. The example of the cache hierarchy in Sandybridge architecture from Intel is in the figure 2.3.

Cache miss typically introduce a time miss penalty, because cache first checks whether it contains the item and only then advances to the next level in the hierarchy. Time to retrieve uncached data item is the sum of time miss penalties in each cache level and time of the memory access. Due to this some synthetic programs could perform better 2. Background

Figure 2.3. Multi-level caching on Intel Sandybridge.

Level 1 cache is the closest to the execution unit, it has the shortest access time, but it is the smallest cache. Caches farther from the execution units are slower, but they can hold more data.

with caches turned off completely. The potential increase in data access time is a risk factor for the real-time systems.

The power of caches lies in the locality of reference. Temporal locality describes phenomena where the same values or memory locations are frequently and repeatedly accessed. Spatial locality assumes that when one memory location is referenced it is likely that nearby locations will soon be also referenced. To exploit spatial locality, the bigger chunk of memory is copied into cache than what was requested. The chunk size closely relates to cache organization which is described in the next section.

#### 2.4.2 Cache organization

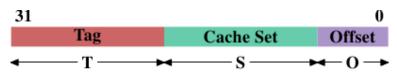

The cache purpose is to capture useful part of the main memory at the given moment. Memories are organized in sequences of data elements – bytes and one byte (1B = 8b;B: byte, b: bit) is the basic addressable unit of memory. In the following, address having the size of 32 bits is considered. The cache needs to know the memory address of the captured element. When the CPU asks for certain address, the cache compares it with addresses associated to the stored elements.

In this paragraph simplistic example is considered, where one cache element allows to store 1B. For such an element there are needed 40 bits (5B) - 4B of information to store 32b address and 1B of data. This would be an inexcusable waste of transistors. Instead, for given address, there are stored multiple data bytes of the memory surrounding such an address. Multiple bytes in cache line is a setup that exploits the spatial locality.

The cache line is the term referencing to basic copiable unit between levels of hierarchy. There are several information fields associated with each cache line such as flags including line validity and bits determining line usage frequency, and further, there is a *tag* as a part of a memory address allowing to refer to the cache line.

Consider cache line with the size of 64B. To refer to the specific byte in the cache line, there is need for 6 addressing bits (indeed  $2^6 = 64$ ). These 6 bits are cut from the end of an address, and they are called the *offset*. The rest 26 bits of the address are used to reference the cache line, and they are called the *tag*. This is the example of **fully associative cache**. The cache stores each tag that is not yet in it to the next

Figure 2.4. Address parts driving cache data element choice. [8]

empty cache line along with its data. Retrieving cache line requires comparison of the input tag to each cache line tag, so the comparator is needed for each cache line.

Besides offset another portion of bits can be cutted from the address and use to address cache lines. Such a portion of bits is called *index* or *cache set*. If each *set* addresses exactly one cache line, then the cache is called **direct-mapped cache**. For example, if the offset is 6 bits long yielding 64B long cache line and the *set* is 8 bits long yielding 256 cache lines the size of the direct-mapped cache is 16kB. Considering 32 bit addresses the size of *tag* is 18 bits long, and only one comparator is necessary to compare *tag* of selected cache line with the input address tag. Every two addresses having same bits in the field *set* end up in the same cache line and replace each other's data. To address this problem, the associativity of the cache must be increased as described in the next paragraph.

By combining the two previous approaches the **set-associative cache** is constructed. The field *set* in the address refers to multiple cache lines. The cache lines in the given set are called ways. According to the number of ways this type of cache is also called **n-way associative cache**. If there are 2 ways in the cache, where for certain *set* one way has already valid cache line, and there is need to store another cache line to the same *set*, it is stored in the second, empty way. Now if the third request comes that has different *tag* but the same *set*, the cache line in one of the two ways have to be replaced. If the cache had more ways than 2 the replacement would not be necessary, cache line would be stored in any empty/invalid way. There are *n* comparators used in this cache type corresponding to number of ways. Modified example from the previous paragraph (64B long cache line and 256 cache lines) with 2 ways would have the size of cache equal to 32kB. Note that none of the address parts (offset, set, tag) sizes have changed.

Caches which have associativity greater than one uses various replacement strategies to a select cache line to be sacrificed when lines in all ways are valid. Among strategies mentioned in literature belong random replacement, Least Recently Used (LRU), Least Frequently Used (LFU), Adaptive Replacement Cache (ARC) combining previous two or Not Recently Used (NRU). These strategies developed in the era of single-core processor. In the multi-core processors, it seems that for per-core private caches the best replacement policy is LRU [9]. There is ongoing research targeting replacement strategies for caches shared by multiple cores in multi-core processors [10–11].

#### 2.4.3 Writing data back to main memory

When the processor writes data to the given address, it might not end up in the main memory right away. Data typically stay in the cache for the moment and get to the main memory later.

- *write through*: policy writes data to the cache, and to the write buffer. From the write buffer data are moved to the main memory asynchronously.

- *write back*: policy writes data to the cache line marking them with flag *Dirty*. When the cache line is canceled the data are moved to the main memory.

#### 2.4.4 Cache inclusion policy

Inclusion policy characterizes relation between adjacent cache levels. It specifies requirements on the presence of the cache line in higher level of hierarchy when it is present in lower hierarchy level.

There are three possible policies:

- *inclusive*: higher level cache is inclusive of lower level cache if the cache line present in lower level cache have to be present also in higher level cache

- *exclusive*: higher level cache is exclusive of lower level cache if the cache line present in lower level cache must not be present in the higher level cache

- non-inclusive non-exclusive: neither of the above two is required

#### 2.4.5 Cache coherency

Since there are per-core private caches in multi-core systems, with parallel programming, it might occur that same data are loaded into two or more caches associated with different cores. If one core modifies data in its cache, it is necessary to inform other cores' caches about the change. Otherwise the incoherency makes the whole system fairly unusable.

If the private caches are interconnected with higher cache level using common bus, the invalidation may be utilized. When one core writes to given address, this address is announced as invalidated on the bus. Cores monitor events on the bus. If the core is not the originator of the announcement, it checks whether its cache contains cache line with the announced address and in case it does the cache line is invalidated.

Another approach is to send updated information. Cores read update requests on the bus, and if the request contains common data, the core updates them in its cache.

Further, more sophisticated protocols such as MOESI and friends may be utilized. Each cache line has information about its coherency state. The possible states in MOESI protocol are briefly described in table 2.1. The protocol then assures that the caches are coherent given the set of allowed states for any pair of caches in the system.

| state     | brief description                                     |

|-----------|-------------------------------------------------------|

| Modified  | This cache has the only valid copy of the cache line. |

| Owned     | There are several caches with the valid copy,         |

|           | but this one has exclusive write permission.          |

| Exclusive | This cache has the only copy.                         |

| Shared    | This cache line can be only read.                     |

| Invalid   | This cache line is invalid.                           |

Table 2.1. MOESI cache coherency protocol states. The validity relates to the given cache line.

#### 2.4.6 Caches incorporated in virtual address model

Up until now the caches were described as a mean to mediate faster access to the portion of memory. Caches are also utilized to speed up some other mechanisms used in current systems.

Nowadays there is widely present memory virtualization in the contemporary systems. With this mechanism it seems to an application as it has whole memory just for itself. It is achieved by providing each app with its own virtual memory (VM). Only small, currently used, portion of program and its data located in VM is actually mapped to the physical memory. The currently unused portions of program and its data are stored in the secondary device (hard drive). The mechanism simplifies management of concurrenly running applications as their address spaces do not collide with each other.

Virtual memory is typically implemented using paging which is managed by OS. With paging the physical address space (main memory) is divided to the regions of equal size called frames. Virtual memory is also divided to the regions of equal size, but these are called pages. Size of frame and page is equal. The size of page in current systems ranges from traditional 4kB all the way up to 16GB. It is always power of 2 as this choice allows to divide the address space equaly.

Simple synthetic example that follows will clarify the behavior of the virtual memory. Consider our virtual space consists of 100 pages and physical memory is divided into 100 frames. Now consider applications – A1 utilizing 60 pages within its 100 page VM and A2 utilizing 70 pages within its 100 page VM. OS starts A1 which uses 60 pages that are mapped (loaded) to arbitrary 60 frames. While A1 is running it needs only 20 pages, because there was possibly only initialization code in other 40 pages. Now the OS starts A2. A2 needs 70 pages to overcome initializations and to get to its regular operation mode. There are still 40 empty frames in physical memory. Further there are 40 frames loaded with 40 pages belonging to A1 that were not used for the long time. 30 of these pages may be stored to the hard drive so that frames become free for use by A2.

Continuing in previous example the sizes of virtual and physical spaces may vary. By lowering the amount of physical memory to 10 frames, the mechanism would still work, but it would be considerably slower due to the necessity to move the pages between frames in main memory and the secondary device. On the other hand if there were 1000 frames available there could be loaded basically 10 applications without need to use of secondary device given the apps utilize fully its 100 pages virtual memory.

Virtual memory wouldn't bring such improvement without support for management structures in hardware. There is need for page tables allowing translation from virtual to physical address. Each process has its own page table structure. When translating virtual memory address to physical memory address, part of the virtual address is used as an index to select entry within page table. The remaining part of the virtual address is an offset within page/frame itself. Among others the page table entry may contain following informations: frame number, where the page is loaded, presence of the page (in memory or swapped out to the secondary device), some privilege information (writable, executable), and some usage statistics.

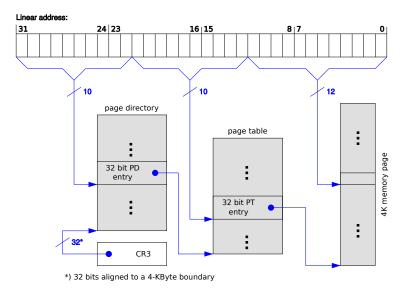

When pages have relatively small sizes, the page table would be very big. To prevent this, page table is split to the hierarchy of page tables. In figure 2.5 is an possible example of hierarchical paging on x86 platform.

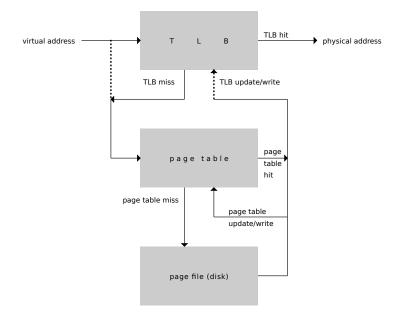

As can be seen from the x86 example to read from or write to physical address there are necessary three accesses to the memory. First it is necessary to read page directory entry, after that page table entry, and finally physical address is obtained and it is accessed. Memory accesses take a long time therefore the translations from virtual page number to the physical frame number are cached in so called Translation Lookaside Buffer (TLB) which may be implemented as CAM. On inserting virtual address it returns physical address or reports cache miss. In figure 2.6 is depicted translation of virtual address to physical address utilizing TLB. The TLB may be divided to instruction cache – ITLB and data cache – DTLB which increases hit rate [13]. There are compared caches of contemporary systems in the table 2.2. Both virtual and physical

Figure 2.5. Paging with 4kB long pages on x86 architecture in 32-bit protected mode. [12]

The OS fills CR3 register with the base address of application's page directory. Linear address is Virtual address after applying x86 segmentation mechanism. Segmentation nowadays typically maps addresses one to one and we won't further elaborate on this. First 10 bits of the Linear address are used to point to entry within page directory, which effectively select the page table – the base address of the page table is stored in the entry. Next 10 bits of the Linear address are used as an index that selects an entry within the page table. PT entry contains frame number within main memory where the program's page is loaded. Remaining 12 bits of the Linear address points to the byte within 4kB long page. Notice the PDs and PTs are also 4kB long therefore they fit in the frames. PDs and PTs may also be swapped out to the secondary device.

addresses are used to select L1 cache item in the Intel platforms. This way cache set may get ready during the time physical address is retrieved from the TLB.

#### 2.4.7 Caches in contemporary hardware

The comparison of currently used caches is best made based on their parameters, which can be seen in table  $2.2.^{1(2)3(4)}$

Interesting Intel's feature is the usage of adaptive cache allocation mechanism for their shared cache. Marketing name is Intel Smart Cache. If only one core is active, it can utilize the whole shared cache.

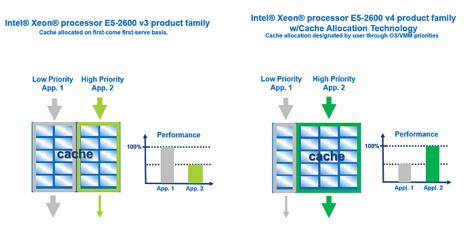

#### **2.4.8** Quality of service in relation to cache

In general the possibility to monitor the cache utilization on the per-thread basis allows the operating system (OS) or hypervisor (HV) / virtual machine monitor (VMM) to reschedule tasks in a way to favor high-priority task. Incremental step is allocating the portion of the cache for such high-priority task.

<sup>1)</sup> http://www.7-cpu.com/

<sup>&</sup>lt;sup>2)</sup> https://stackoverflow.com/questions/33974193/does-x86-64-cpu-use-the-same-chache-linesfor-communicate-between-2-processes-vi

<sup>&</sup>lt;sup>3)</sup> http://www.realworldtech.com/sandy-bridge/7/

$<sup>^{\</sup>rm (4)}$  https://superuser.com/questions/745008/whats-the-difference-between-physical-and-virtual-cache

Figure 2.6. Principle of TLB and illustration of Page Table miss. [12]

When TLB has virtual address cached it responds with physical address. If the physical address can't be obtained from the TLB there is need to do a page walk. If either page table or target page is not present in the memory, OS loads them from the hard drive to the main memory. Then the physical address is obtained using the paging mechanism, the record is created in the TLB (i.e., VA is cached) and the physical address is passed to the next stage.

An implementation of cache QoS is available for example in the Intel Resource Director Technology RDT. The details on the RDT are available in section 3.2.3. Another example utilizing QoS in relation to cache could be Qualcomm's Centriq 2400<sup>1</sup>).

<sup>&</sup>lt;sup>1)</sup> https://www.anandtech.com/show/11737/analyzing-falkors-microarchitecture-a-deep-diveinto-qualcomms-centriq-2400-for-windows-server-and-linux/2

2. Background

|           | I          |            |                        |           |            |

|-----------|------------|------------|------------------------|-----------|------------|

|           | Intel      | Intel      | IBM                    | ARM       | AMD        |

|           | Haswell    | Skylake    | POWER8                 | Cortex-A1 | Jaguar     |

| L1 data   | 32 KB      | 32 KB      | 64 KB                  | 32 KB     | 32 KB      |

|           | 64 B/line  | 64 B/line  | 128  B/line            | 64 B/line | 64 B/line  |

|           | 8-WAY      | 8-WAY      | 8-WAY                  | 2-WAY     | 8-WAY      |

| - indexed | virtually  | virtually  |                        |           |            |

| - tagged  | physically | physically |                        |           |            |

| L1 instr. | 32 KB      | 32 KB      | 32 KB                  |           | 32 KB      |

|           | 64 B/line  | 64  B/line |                        |           | 64  B/line |

|           | 8-WAY      | 8-WAY      | 8-WAY                  |           | 2-WAY      |

| - indexed | virtually  | virtually  |                        |           |            |

| - tagged  | physically | physically |                        |           |            |

| L2 cache  | 256  KB    | 256  KB    | 512  KB                | 1 MB      | 2  MB      |

|           | 64 B/line  | 64 B/line  | 128  B/line            | 64 B/line | 64 B/line  |

|           | 8-WAY      | 4-WAY      | 8-WAY                  | 16-WAY    | 16-WAY     |

|           | NINE       | NINE       |                        |           |            |

| - indexed | physically | physically |                        |           |            |

| - tagged  | physically | physically |                        |           |            |

| L3 cache  | 8 MB       | 8 MB       | 8 MB                   |           |            |

|           | 64 B/line  | 64 B/line  | $128 \mathrm{ B/line}$ |           |            |

|           |            | 16-WAY     | 8-WAY                  |           |            |

|           | inclusive  | inclusive  |                        |           |            |

| - indexed | physically | physically |                        |           |            |

| - tagged  | physically | physically |                        |           |            |

| - taggeu  | physically | physically |                        |           |            |

**Table 2.2.** Cache parameters of contemporary hardware platforms.Note: some specific model parameters may vary.

### 2.5 Performance Monitor Unit (PMU)

PMU is a logical component of the processor. PMU serves the purpose of capturing and reporting summaries of various performance events. With this component it is possible to profile applications. It is possible to measure characteristics such as cache misses, cache accesses, memory accesses, and others.

The value of the measured event is counted in the performance monitor counter. There is limited amount of the counters available on platforms and each counter has configuration register. To start counting event its number needs to be set in the configuration register of the selected counter.

When reading core specific value such as L1 cache characteristics, on typical platform it is necessary to read the register using given core.

## 2.6 Hypervisor

A hypervisor (HV) is virtual machine manager and monitor. Typically the hypervisor manages multiple instances of virtual machines running on one physical computer. Such a computer needs to support hardware virtualization (otherwise the virtualization would be significantly slower). Virtual machines called guest machines run operating systems and guest OSes run in turn the target applications.

Hypervisor running on host machine manages the hardware and provides guests with access to the hardware. Since there exist cases of one instance of hardware (for example

there is typically only one instance of the ethernet interface) the HV provides guests with virtualization of such a hardware so that each can access such a scarce resource. Typical HV may also schedule accesses to the shared resources. When such a resource is currently assigned to one VM another VM has to wait until the scarce resource becomes available.

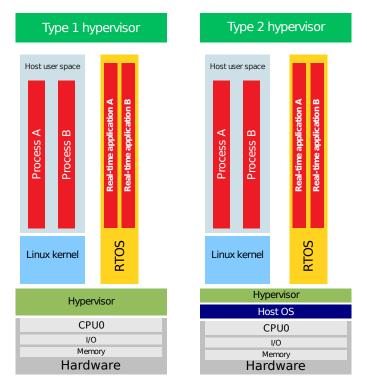

Historically hypervisors were classified as Type-1 for native hypervisors running on bare metal and Type-2 hypervisors as an application under host operating system [14]. Figure 2.7 highlights the difference.

Figure 2.7. Hypervisor types comparison. [15]

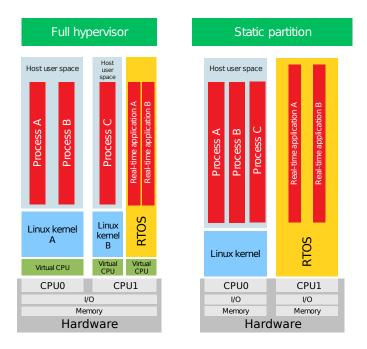

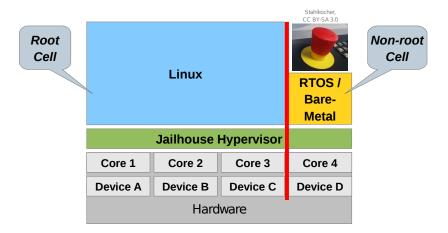

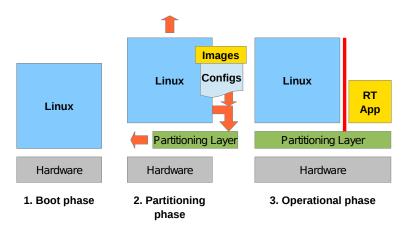

#### **2.6.1** Hardware partitioning

With the generic hypervisor there are hardware resources shared among VMs. The scheduling of access to the hardware is a contention point and potentially source of time unpredictability. The solution to overcome such unpredictabilities that may be employed is partitioning hardware with the supervision of hypervisor. The contention point is removed by dedicating certain hardware to certain VM. With this setup there can be a set of real-time tasks, each in its own VM with preallocated hardware resources necessary for the task's operation. The tasks are separated from each other and the risk of one task interfering with another is lowered significantly.

To perform beneficial task, the machine, in our case virtual machine, needs at least some memory for data and code, execution unit, and output device. If supported by the HV (and by HW), the following resource may be partitioned and assigned to virutal machines:

- processor cores

- cache

- memory

- input/output ports (on x86)

2. Background

Figure 2.8. Comparison of virtualization types. [15]

- memory mapped input/output devices

- PCI devices

- UARTs

- VGA text console

- IRQ chips

The hardware partitioning may be also called static allocation of resources. Compare full hypervisor with static partitioning hypervisor in figure 2.8. [16]

### 2.7 PRedictable Execution Model (PREM)

This section is based on the knowledge of Real-time systems that were described in section 2.1 and contemporary memory systems described in section 2.4.

In a typical computer system, there are several execution units – processor cores and other subsystems that share the main memory and contest for the main memory bandwidth. If two or more resources request access to the main memory at the same time, one of them gets the access while the others are stalled. Considering real-time systems requirement for predictability this behavior is undesirable due to its unpredictability. An execution unit might miss its deadline while waiting for the data. To address this problem, time slots could be allocated for each device in which it can access memory so that the access is dedicated and schedulable. That is exactly the main idea behind PRedictable Execution Model (PREM) – the ability to coschedule all active components (e.g., CPU cores, I/O peripherals) in the system at a high level. [17]

Each device has its time slot where it can access the needed data for further processing, but obviously, the device itself must have some local storage to bridge the time interval when it has no access to the main memory. There are two local storage options discussed in the literature that can be used for this purpose in CPUs – scratchpad memories (SPMs) and caches. Scratchpad memory is fast and small on-device memory (SRAM) addressable directly from the device itself. Unlike cache, SPM is not transparent to the programmer, thus either programmer or compiler must issue instructions to load data into the scratchpad memory before processing them. SPM may be either mapped to global or separate address space, where the latter is more likely [18]. SPMs are not part of the mainstream hardware, so we will not discuss them further.

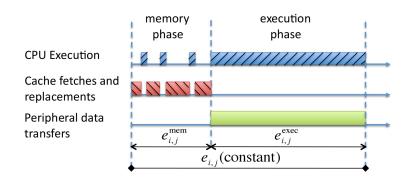

Figure 2.9. Model of a task in task-based execution system.

There is predictable time interval with constant execution time. In the memory phase CPU loads all data it needs and processes them in the execution phase. While CPU core is processing data memory is free to be accessed by peripherals (e.g., GPU) or other cores.  $e_{i,j}^{mem}$  is the time duration of memory phase and  $e_{i,j}^{exec}$  is the time of execution phase, where index *i* marks task number and since each task is divided into scheduling intervals those are numbered with index *j*. [17]

Pellizzoni et al. [17] describe how to schedule tasks with I/O operations, so that whole system execution is predictable while using COTS platforms. Two classes of intervals are scheduled. Compatible intervals are compiled and executed in no particular manner. Within compatible intervals I/O data flows are not allowed, there are allowed only I/O interrupts of peripherals associated with given task. Predictable intervals have two phases as depicted in figure 2.9 – during memory phase data are exchanged between main memory and cache of the corresponding CPU, and during the execution phase, the data loaded into caches are processed. The I/O operations accessing main memory are also scheduled in the execution phase.

There was created a PREM real-time C compiler [17]. Macros are used by the programmer to mark parts of predictable interval function. With the help of these annotated intervals compiler passes transform the interval to be predictable. The PREM compiler source code is not publicly available.

#### 2.7.1 WCET-aware compiler

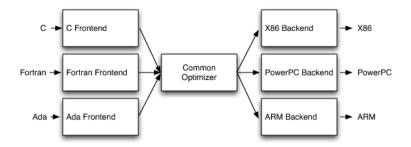

A compiler is a program that translates executable source code in one language to an executable source code in another language. Traditional compilers have two parts – frontend and backend. In this setup, the frontend translates source code into intermediate representation (IR), IR is optimized in case of optimizing compiler, and finally, the backend translates IR to the machine code.

With the IR in the middle the compiler becomes extensible more easily. To add support for another language only the frontend needs to be modified. Similarly to add support for the different target machine, the new backend needs to be added. This 2. Background

Figure 2.10. Multi-target compiler.

On the left, there are frontends for different languages that get transformed to the compiler intermediate representation (IR). IR is optimized and transformed to the target machine code by the appropriate backend.

approach makes the IR important part of the compiler. Insightfully designed IR can be optimized well, and that leads to somewhat better output programs than the original.

The goal of optimizations is to make the code better in some way. The programs can be optimized for speed when running, for the size of the resulting code, for energy efficiency, and for other purposes. IR is not the only stage that can be optimized. The resulting machine code is another stage where the optimization opportunity occurs. However, these optimizations require more effort since the stage needs to be reimplemented for each backend.

#### 2.7.2 Decoupled Access Execute (DAE)

The approach that divides the execution into phases that are called *access phase* and *execute phase* is described in work of Koukos et al. [19]. These phases are analogic to the *memory phase* and *execution phase* in PREM [17]. Authors of DAE use the separated phases to optimize the energy efficiency of general purpose programs. They utilize hardware capability Dynamic Voltage and Frequency Scaling (DVFS) to decrease frequency during access phase when the data are preloaded from the main memory to the cache. The slow down in this phase is negligible since the processor waits for the data to be fetched anyway. Execute phase runs using high frequency. The results show that for memory-bound applications there are improvements not only in energy efficiency but the applications even run faster.

# 2.8 MemGuard: limiting memory bandwidth of CPU cores

MemGuard is a tool for memory performance isolation. It serves as an efficient memory bandwidth reservation system. "MemGuard distinguishes memory bandwidth as two parts: *guaranteed* and *best effort*." [5] "It improves system throughput by exploiting best effort bandwidth after each core satisfies its guaranteed bandwidth." [5] As MemGuard operates with available resources it needs to be implemented within OS or VMM.

Memory performance isolation means "that the average memory access latency is no larger than when running on a dedicated memory system" [5]. Potential delay in the DRAM controller can be minimized by regulating the per-client aggregated requests to the DRAM controller. This comes from the fact that thanks to MG the sum of bandwidth from all the clients is less than or equal to the possible memory bandwidth and so the memory requests are likely to be processed immediately.

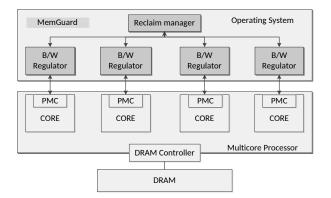

Figure 2.11. MemGuard system architecture. [5]

"The per-core regulator is responsible for monitoring and enforcing its corresponding core memory bandwidth usage. It reads the hardware PMC to account the memory access usage. When the memory usage reaches a predefined threshold, it generates an overflow interrupt so that the specified memory bandwidth usage is maintained. Each regulator has a history based memory usage predictor. Based on the predicted usage, the regulator can donate its budget so that cores can start reclaiming once they used up their given budget. The reclaim manager maintains a global shared reservation for receiving and re-distributing the budget for all regulators in the system. " [5]

MemGuard consists of two main components: the per-core regulator and the reclaim manager. Its design is described [5] along with the design outline in figure 2.11.

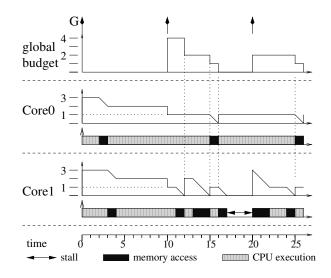

The budget assigning example and its cited [5] description in figure 2.12 helps to understand how MemGuard operates.

2. Background

Figure 2.12. MemGuard budget illustrative example with two cores. [5]

"Each core has assigned static budget 3 (i.e.,  $Q_0 = Q_1 = 3$ ). The regulation period is 10 time units and the arrows at the top of the figure represent the period activation times. The figure demonstrates the global budget together with these two cores.

When the system starts, each core starts with the assigned budget 3. At time 10, the prediction for each core is 1 as it only used budget 1 within the period [0,10], hence, the instant budget becomes 1 and the global budget G becomes 4 (each core donates 2). At time 12, Core 1 depletes its instant budget. Since its assigned budget is 3, Core 1 tries to reclaim 2 from G and G becomes 2. At time 15, Core 1 depletes its budget again. This time Core 1 already used its assigned budget, only a fixed amount of extra budget ( $Q_{min}$ ) 1 is reclaimed from G and G becomes 1. At time 16, Core 0 depletes its budget. Since G is 1 at this point, Core 0 only reclaims 1 and G drops to 0. At time 17, Core 1 depletes its budget again then it dequeues all the tasks as it can not reclaim additional budget from G. When the third period starts at time 20, the  $Q_1^{predict}$  is larger than  $Q_1$ . Therefore, Core 1 gets the full amount of assigned budget 3, while Core 0 only gets 1, and donates 2 to G. At time 25, after Core 1 depletes its budget, Core 1 reclaims an additional budget  $Q_{min}$  from G." [5]

# 2.9 Page coloring as a software solution addressing cache contention

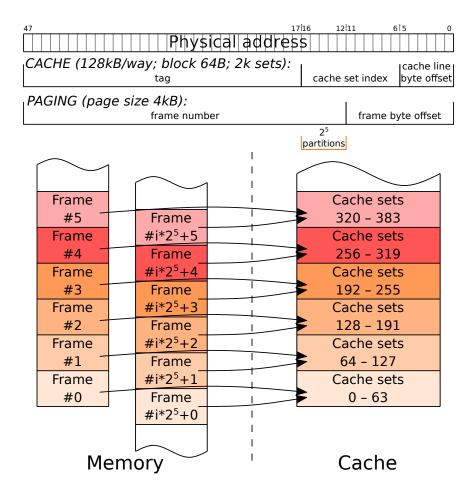

One cache contention solution was addressed in the section 3.2.3 dedicated to cache partition supported in hardware using Intel RDT. Another purely software method to partition cache that I want to mention is Page Coloring [7, 13]. An example explaining the principle of the matter is in figure 2.13. This software based cache partitioning may be enabled when there is support in the OS or the Hypervisor.

Figure 2.13. Example of page coloring used to partition cache.<sup>[7]</sup>

Consider system with the following parameters. Physical address is 48-bits long. Pages of virtual memory are 4kB in size. Cache is indexed using physical address. It has 128kB per way, its block size is 64B, and it has 2048 sets.

All the frames that have low 5 bits of frame number in common are cached in specific portion of 64 cache sets. In this example there may be total of  $2^5 = 32$  partitions. The bits that determines partition number are referred to as *page color*[7]. Virtual memory manager has to ensure client of the partitioning has its virual pages mapped into frames with numbers following this formula:  $i * 2^n + p$ , where  $i \in \aleph_0$ ,  $n = log_2(number\_of\_cache\_sets) + log_2(cache\_line\_size) - log_2(page\_size)$ , and per client chosen partition  $p \in \langle 0; 2^n \rangle$  Notice the page size have to be less than cache size in one way for the partitioning described to be possible.

The chapter describes:

- used hardware platforms

- evaluation hypervisor Jailhouse

- design of experiments

The description of evaluation platforms includes NVIDIA TX2 and Intel Xeon W. System on chip Tegra X2 made by NVIDIA is to be found in section 3.1. The platform to evaluate cache partitioning effects is Xeon W processor from Intel described in 3.2.

## 3.1 NVIDIA Tegra X2

The primary platform used to evaluate methods increasing time predictability is the Jetson Tegra X2 made by NVIDIA. At a time, it was marketed as "the fastest, most power-efficient embedded AI computing device" <sup>1)</sup>. There is a summary of parameters of the TX2 SoM in the table 3.1.

A variant of this platform is used in the applications such as Tesla Motors' self-driving capability <sup>2)</sup> or infotainment system of the Mercedes-Benz <sup>3)</sup> and others.

| parameter             | value                      |

|-----------------------|----------------------------|

| Power consumption     | < 15 Watts                 |

| Main memory           | 8 GB LPDDR4                |

|                       | 128-bit bus                |

| Peak memory bandwidth | 59.7  GB/s                 |

| CPU                   | NVIDIA Denver2 (dual-core) |

|                       | ARM Cortex-A57 (quad-core) |

| GPU                   | Pascal (256-core)          |

| SW support            | Ubuntu 16.04               |

|                       | Kernel 4.4                 |

Table 3.1.

Selected parameters of the Tegra X2 system on module.

TX2 platform is used in this work to see the effects of memory bandwidth throttling on the level of memory controller. We want throttle especially the GPU to ensure certain level of memory bandwidth is available for the CPUs. The throttling of the GPU on the memory controller level was previously done and used on the TX1 platform. Further we evaluate the concept of MemGuard on this platform. The MemGuard implementation is dependent especially on the CPU's Performance Monitor Unit (PMU). Therefore

<sup>&</sup>lt;sup>1)</sup> https://developer.nvidia.com

<sup>&</sup>lt;sup>2)</sup> https://electrek.co/2017/05/22/tesla-nvidia-supercomputer-self-driving-autopilot/

<sup>&</sup>lt;sup>3)</sup> https://blogs.nvidia.com/blog/2018/01/09/mercedes-ces-2018/

further sections focus especially on the description of memory controller of the TX2 platform and the PMUs used.

Note: The documentation [20] of the TX2's memory controller is rather sparse whereas the TX1's memory controller is documented in its manual [21] substantially better. From the comparison of register descriptions in both documentations follows that the MC of TX2 is heavily based on the one of TX1. Therefore we use TX2 documentation as an incremental documentation above TX1 docs. Some MC registers are completely left out of the TX2 documentation. As an example of the omitted registers those related to PTSA could be mentioned. There exists another source allowing to check which registers are available on the platform and it is the Linux kernel headers provided by NVIDIA.

For the overlapping MC design of the TX1 and TX2 discussed in previous paragraph, sources from both platforms' documentations are compiled to describe memory controler in coming sections.

#### **3.1.1** System organization

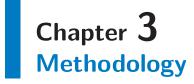

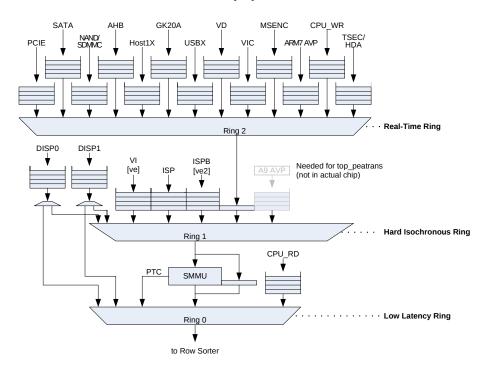

TX2 platform is based on the Parker series processor. Its block diagram may be seen in the figure 3.1.

The module utilizes shared memory over all data consumers i.e., CPUs and GPU access the same physical memory, meaning there is no dedicated memory for the GPU.

Figure 3.1. Block Diagram of a Parker series processor. [20]

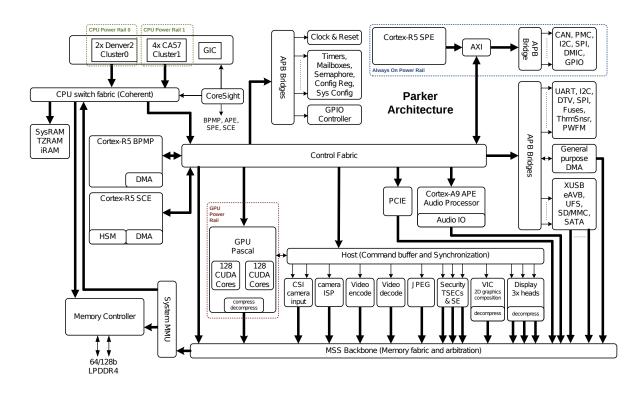

#### **3.1.2** Memory subsystem

There are several technical means utilized when moving data along the path from the main memory (DRAM) modules to the consumers of the data and back. It includes components that are described in the following paragraphs. The scheme of the memory controller components is in the figure 3.2. Following terms are taken over from [20].

3. Methodology