## CZECH TECHNICAL UNIVERSITY IN PRAGUE

Faculty of Electrical Engineering Department of Control Engineering

## Vehicle test platform

Master's thesis

Study program:Open informaticsMajor:Computer engineeringSupervisor:Doc. Ing. Jiří Novák, Ph.D.

Martin Zeman

I confirm that I've completed this thesis myself and have only used the sources (including literature, projects and software) listed in the corresponding section.

In Prague 30.12. 2014

signature

## Abstrakt

Tato práce si klade za cíl návrh struktury a implementaci programového vybavení pro testovací platformu vozidlových komunikačních standardů. Náplň se skládá z vývoje obslužné aplikace pro platformu PC Windows. Další součástí je firmware řídicího mikrokontroléru samotné platformy postavený nad operačním systémem reálného času. K propojení obou části je zapotřebí navrhnout komunikační protokol pro jejich interakci. Systém musí být schopen vzdálené rekonfigurace hradlového pole, jež je součástí testovací platformy a obsluhy řadičů standardu FlexRay v něm implementované.

## Abstract

This thesis aims to design the structure of and to implement the software component of a test platform for vehicular communication standards. The task breaks down into two main areas. The first entails the development of a PC platform-based application responsible for coordinating all platform functionality. The second part involves the development of firmware on the platform side. The system is required to run a real-time operating system. In order to enable interaction between the parts a communication protocol needs to be developed. The system must be capable of remote reconfiguration of the design in the FPGA, which is a part of the platform.

## Acknowledgements

First and foremost a sincere thank you goes to Doc. Ing. Jiří Novák, Ph.D. I appreciate his patience and time devoted to helping me succeed. I'm equally grateful for his tolerance for broken hardware. I'd also like to thank my friend and former classmate Ing. Jiří Blecha, the author of the platform's hardware, for always taking the time to explain the intricacies of his design. Last but not least, I express my gratitude to my family who have supported me during my studies and continue to do so.

# **Table of contents**

| Abstrakt     |                               |

|--------------|-------------------------------|

| Abstract     |                               |

| Acknowled    | gements                       |

| Table of co  | ntents1                       |

| List of figu | res and tables4               |

| 1. Introd    | uction1                       |

| 1.1. A       | analysis of the assignment    |

| 1.2. A       | analysis of the solution      |

| 2. FlexR     | ay3                           |

| 2.1. B       | brief description             |

| 2.2. P       | hysical layer4                |

| 2.3. L       | ink layer                     |

| 2.3.1.       | Architecture of a node        |

| 2.4. C       | Communication cycle           |

| 2.4.1.       | Microtick – $\mu$ T           |

| 2.4.2.       | Macrotick – MT 11             |

| 2.4.3.       | Static segment                |

| 2.4.4.       | Dynamic segment               |

| 2.5. F       | rame format                   |

| 2.6. C       | Clock synchronization         |

| 2.6.1.       | Measurement                   |

| 2.6.2.       | FTM algorithm14               |

| 2.6.3.       | Rate Correction calculation   |

| 2.6.4.       | Offset correction calculation |

| 2.7. S       | tartup mechanism              |

| 3. Syster    | n architecture                |

| 4. FreeRTOS                                      |  |

|--------------------------------------------------|--|

| 4.1. Port settings                               |  |

| 4.2. Features used                               |  |

| 4.2.1. Tasks                                     |  |

| 4.2.2. Queues                                    |  |

| 4.2.3. Mutexes, semaphores and binary semaphores |  |

| 5. Firmware                                      |  |

| 5.1. Porting of the lwIP stack                   |  |

| 5.2. Command processing                          |  |

| 5.3. Task declaration macros                     |  |

| 5.4. TCP server implementation                   |  |

| 5.5. EMIF                                        |  |

| 5.6. MCU state machines                          |  |

| 5.6.1. MCU Connection state machine              |  |

| 5.6.2. MCU FR state machine                      |  |

| 5.6.3. FPGA FR state machine                     |  |

| 6. PC Application                                |  |

| 6.1. State machines                              |  |

| 6.1.1. General state machine                     |  |

| 6.1.2. FPGA State Machine                        |  |

| 6.2. Features                                    |  |

| 6.2.1. Monitoring and frame transmission         |  |

| 6.2.2. Remote reconfiguration of the FPGA        |  |

| 6.2.3. Remote task control                       |  |

| 6.2.4. Fibex parsing                             |  |

| 6.2.5. FPGA FlexRay controller and Testing       |  |

| 6.2.6. Target I.P. setting                       |  |

| 6.2.7. ECU Mapping                               |  |

| 6.2.8     | 8. Saving and loading of Cluster and MCU parameters | 48 |

|-----------|-----------------------------------------------------|----|

| 6.2.9     | 9. Other useful features                            | 49 |

| 6.3.      | TCP client implementation                           | 51 |

| 6.4.      | Database                                            | 51 |

| 7. Con    | nmunication protocol                                | 55 |

| 7.1.      | Purpose of the protocol                             | 55 |

| 7.2.      | Requirements                                        | 55 |

| 7.3.      | Negotiation of supported functions                  | 56 |

| 7.4.      | Message format                                      | 56 |

| 7.4.1     | 1. PC to MCU                                        | 57 |

| 7.4.2     | 2. MCU to PC                                        | 64 |

| 8. Con    | nclusion                                            | 66 |

| Reference | es                                                  | 67 |

# List of figures and tables

## List of Figures

| Figure 2-1: FlexRay transceiver with two channels                     |

|-----------------------------------------------------------------------|

| Figure 2-2: Levels of FlexRay's electrical signals                    |

| Figure 2-3: A Bus with two channels                                   |

| Figure 2-4: Dual channel single star configuration                    |

| Figure 2-5: Single channel cascaded star configuration                |

| Figure 2-6: Dual channel cascaded star configuration7                 |

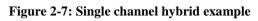

| Figure 2-7: Single channel hybrid example7                            |

| Figure 2-8: Dual channel hybrid example                               |

| Figure 2-9: Physical layer and link sub-layers9                       |

| Figure 2-10: Architecture of a FlexRay node                           |

| Figure 2-11: Communication cycle                                      |

| Figure 2-12: FlexRay frame format                                     |

| Figure 2-13: An example of FTM calculation for $k = 2$                |

| Figure 3-1: System architecture                                       |

| Figure 5-1: Command dispatching                                       |

| Figure 5-2: EMIF Settings                                             |

| Figure 5-3: MCU Connection state machine                              |

| Figure 5-4: State machine for handling the MCU's FlexRay controller   |

| Figure 5-5: Details of message exchange at the end of data definition |

| Figure 5-6: MCU FPGA State machine                                    |

|      | Figure 6-1: PC application's main state machine                                     | 35 |

|------|-------------------------------------------------------------------------------------|----|

|      | Figure 6-2: PC FPGA State machine                                                   | 37 |

|      | Figure 6-3: How to select a frame to be monitored                                   | 38 |

|      | Figure 6-4: Difference between FPGA and MCU frames                                  | 39 |

|      | Figure 6-5: Message Editor tab example                                              | 40 |

|      | Figure 6-6: Monitoring example                                                      | 41 |

|      | Figure 6-7: Remote configuration                                                    | 42 |

|      | Figure 6-8: Task manager window                                                     | 43 |

|      | Figure 6-9: UML diagram of a FlexRay fibex file                                     | 14 |

|      | Figure 6-10: Cluster Setup after loading a fibex file                               | 45 |

|      | Figure 6-11: Cycle settings in the MCU                                              | 46 |

|      | Figure 6-12: FGPA Status window                                                     | 47 |

|      | Figure 6-13: IP Address settings window                                             | 47 |

|      | Figure 6-14: ECU Mapping example                                                    | 48 |

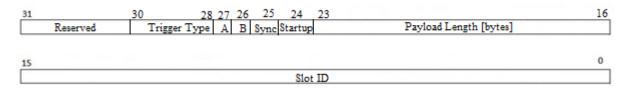

|      | Figure 6-15: Load and Save menu options                                             | 49 |

|      | Figure 6-16: Absolute vs relative time                                              | 50 |

| Exce | Figure 6-17: Monitoring record from Figure 6-6 saved as CSV file and displayed in N |    |

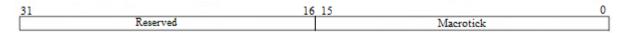

|      | Figure 7-1: MCU slot definition message format - first word                         | 59 |

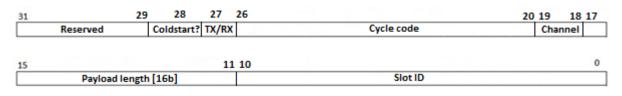

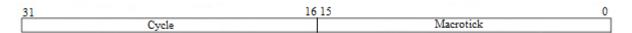

|      | Figure 7-2: MCU slot definition message format - second word                        | 50 |

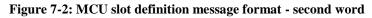

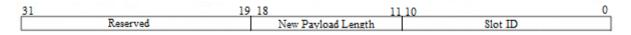

|      | Figure 7-3: MCU Tx Data Definition Message Format                                   | 50 |

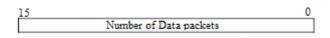

|      | Figure 7-4: MCU Tx Data Update Message Format                                       | 50 |

|      | Figure 7-5: FPGA TX frame data definition message format - first word               | 51 |

| Figure 7-6: FPGA TX frame data definition message format - Timestamp - second and            |

|----------------------------------------------------------------------------------------------|

| third word                                                                                   |

| Figure 7-7: FPGA TX frame data definition message format - Macrotick - second word           |

| Figure 7-8: FPGA TX frame data definition message format - Macrotick and Cycle - second word |

|                                                                                              |

| Figure 7-9: FPGA TX frame data update message format                                         |

| Figure 7-10: Send FPGA design message format - bytes 0 to 363                                |

| Figure 7-11: Send FPGA design message format - bytes 4 to 563                                |

| Figure 7-12: Send FPGA design data message format                                            |

| Figure 7-13: Supported Commands and Version Response message format65                        |

| Figure 7-14: FlexRay Data Message Format65                                                   |

## List of Tables

| Table 2-1: An example of measured values  | 14 |

|-------------------------------------------|----|

| Table 2-2: Number of entries to eliminate | 15 |

| Table 6-1: Contents of the ECUs table     |    |

| Table 6-2: Contents of the FPGAs table    | 53 |

| Table 6-3: Contents of the Frames table   | 54 |

| Table 6-4: Contents of the Signals table  | 54 |

| Table 6-5: Contents of the Triggers table | 55 |

| Table 7-1: PC to MCU command table        |    |

| Table 7-2: MCU FlexRay parameters         | 59 |

| Table 7-3: FPGA FlexRay parameters        | 61 |

| Table 7-4: Trigger Type values                                                  | 62    |

|---------------------------------------------------------------------------------|-------|

| Table 7-5: MCU to PC response table                                             | 64    |

| The three bytes in Figure 7-13 are followed by a number of bytes defined in     | n the |

| Number of commands" section. Each byte contains a supported command code from 7 | Table |

| -1                                                                              | 64    |

# 1. Introduction

## 1.1. Analysis of the assignment

The aim of this thesis is to integrate various projects from a number of authors into a functional and flexible vehicular testing platform. The integration consists of a development of a PC-Windows-based application responsible for providing an interface between the testing platform and the user. The application must be capable of controlling the function of the FlexRay controller present in the platform's MCU such as defining the outgoing communication and monitoring of the incoming frames.

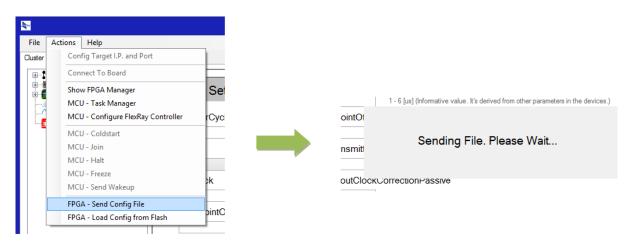

Another important feature is the remote reconfiguration of the design in the FPGA. The application has to be able to send an arbitrary design file from the PC's file system to be loaded into the FPGA or be capable of loading the default design present in the MCU's flash memory.

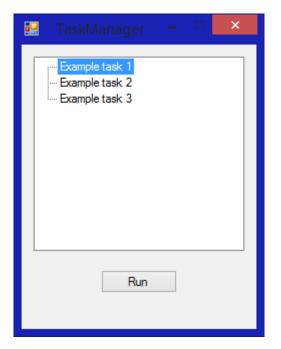

Next, the application needs to provide the functionality to remotely run and suspend user-defined tasks in the MCU. Said tasks are to be defined at compile time as part of the MCU's firmware.

The application is also responsible for the management of the FlexRay controllers implemented in the FPGA. These controllers provide some unique features for the testing of the parameters of the FlexRay networks. The application's role is to trigger these tests and present the user with results. Specifically, the application needs to provide an interface in which to configure and manage all the controllers present in the FPGA separately.

On the hardware side the MCU is required to run a real-time operating system to provide the programmer with methods of task synchronization and resource protection. The use of a real-time operating system also offers a higher flexibility in terms of task separation, better control over timing requirements and an overall richer selection of tools for building non-trivial systems.

The MCU's firmware acts as the execution centre for all the system's functionality. It needs to receive and decode requests from the PC application and carry out corresponding actions. In order to facilitate these functions, it is necessary to develop a protocol for communication between the PC application and the MCU.

1

#### **1.2.** Analysis of the solution

From a hardware standpoint the platform provides a TMS570LS3137ZWT microcontroller from Texas Instruments. This chip has been chosen due to previous experience with it in which it has proven to be both powerful and cost-efficient. The chip provides a wide variety of interfaces and modules, as well as a flash memory of sufficient capacity (3072 KB) for the purposes of the platform.

Another significant advantage of this microcontroller is that Texas Instruments provide developers with a great tool called Halcogen to generate code for its configuration, initiation and libraries for all its peripherals, with the exception of the FlexRay interface. This tool is also capable of generating a port of the freeRTOS real-time operating system specifically for the TMS570 MCU family.

This makes the choice of the real-time operating systems simple. Our requirements for the OS are:

- Real-time capability

- Must be lightweight

- Must be able to provide methods of task-synchronization and resource protection

- Must be able to provide an interface to report defined tasks and run/suspend them flexibly

- Must be free

- Must be open-sourced with a reasonable license

- Needs to be well-documented

FreeRTOS meets all these requirements and therefore has been selected as the OS for the platform. Detailed settings of the used port are described in section 4.1.

The firmware can take advantage of a FlexRay library written for the E-Ray controller by the author of this thesis for a previous project (source [11]). It provides a basic API which simplifies the handling of the controller's functions.

A decision has been made to use the TCP/IP protocol as a basis for building the communication protocol between the PC application and the MCU. The main reason for this decision over the USB, which is in reality the only other candidate, is previous experience with the lwIP stack. Another factor is TCP's simplicity compared to USB. Its advantage

compared to UDP lies in its reliability while maintaining high enough throughputs. This decision requires the lwIP stack to be ported for the combination of freeRTOS with TMS570.

A couple of possible ways to implement the communication protocol between the PC application and the MCU were considered. The first option was to opt for a RPC-type protocol. This category broke down further into binary-based or human-readable protocols, Bert and Apache Thrift are examples of the former and JSON-RPC or SOAP of the latter. The alternative to RPC is a custom-made binary protocol. Considering the rather small computational frequency of the MCU's core (160 MHz) and the number of tasks it has to perform, the XML or JSON-based options needed to be dismissed due to the difficulty of their parsing. A custom binary protocol has been selected since it offers the best performance while maintaining simplicity.

The C# programming language with its .NET framework has proven to be a powerful, flexible and versatile choice for our projects in the past. It offers an easy-to-use networking and database API together with a vast variety of GUI components to build an application that is both user-friendly and visually pleasing. Therefore, it has been chosen for this project as well.

The FlexRay protocol defines a large number of parameters, which are necessary for a network to function. The Fieldbus Exchange Format (FIBEX) is a network description standard defined by the Association for Standardization of Automation and Measuring Systems (ASAM) which encompasses all common automotive communication standards including FlexRay. A FIBEX file contains all the information needed to describe an entire onboard network and has become the standard input file format for commercial software. For this reason, a decision has been made to use FIBEX as the input format for the PC application.

## 2. FlexRay

## 2.1. Brief description

The FlexRay standard is a communication protocol released by the FlexRay Consortium in the year 1999. Members of the consortium are leading companies of the automotive industry such as GM, Bosch, BMW, Motorola, Volkswagen, Freescale, Daimler Chrysler and others. The standard has been developed primarily for the automotive industry.

Its intended field of application lies chiefly in safety-critical applications for instance steer-by-wire or brake-by-wire. In contrast to standards like CAN, TTCAN or LIN it offers higher bandwidth up to 10 Mbit/s. It is based on the time-division multiplexing (TDMA) principle the determinism of which is crucial for real-time applications. This also presents its main advantages over aforementioned standards which use the master/slave (LIN) or CSMA/CR (CAN) methods of arbitration.

However, FlexRay combines both deterministic and stochastic approaches to communication which makes it flexible. The standard only defines the physical and the link layers as defined by the ISO/OSI reference model.

### 2.2. Physical layer

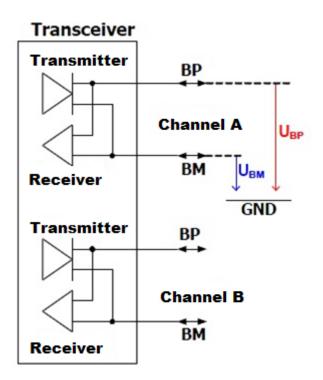

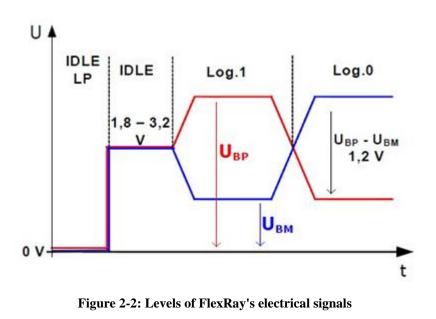

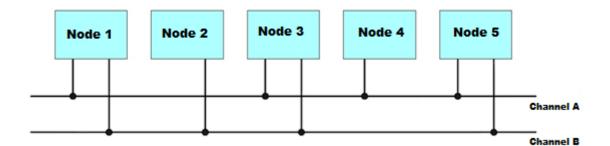

The physical layer is represented by a transceiver and an unshielded twisted-pair cabling. The standard also offers the possibility to use optical fibers with optical transceivers. FlexRay supports the usage of two separate channels (commonly referred to as A and B). Those can act as completely independent media or can provide redundancy to achieve better reliability. However, data consistency on redundant channels isn't secured by the controller intrinsically and thus has to be implemented by the host.

Figure 2-1: FlexRay transceiver with two channels

Source: [1]

Source: [1]

Furthermore, FlexRay introduces the bus guardian. It is an optional part of the physical layer. The bus guardian is an element responsible for the protection of the channel from interference caused by communication that is not in compliance with the cluster's communication schedule. It is capable of blocking outgoing communication in time slots that are not assigned to its hosting node. This prevents a potential break down of communication between all the nodes of a cluster.

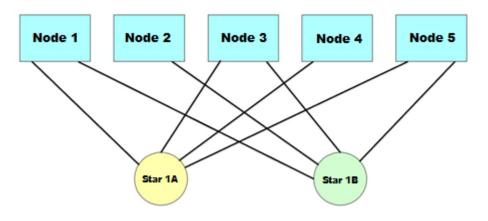

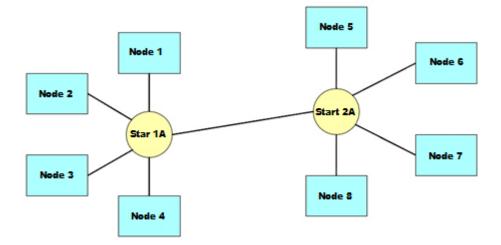

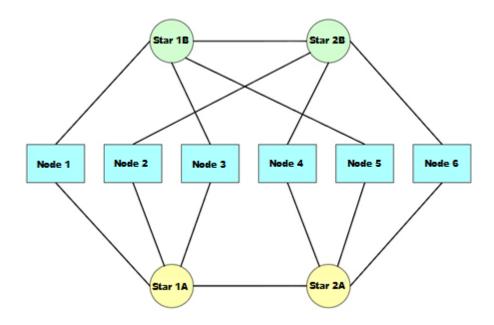

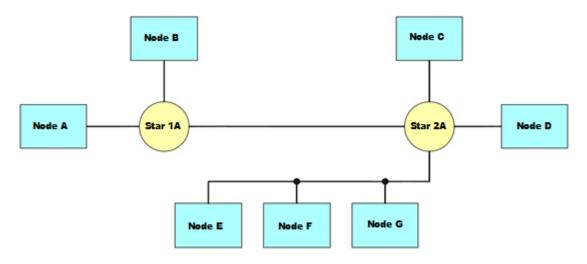

There are several approaches to designing a FlexRay cluster depending on its topology. In addition to pure topologies like a bus or a star, FlexRay also supports their hybrid variants which are a combination of the two. The number of channels used and their configuration presents another point of decision. There's a plethora of possibilities. The thing to keep in mind is the maximum length of a segment between two nodes which is 24 meters. These are some examples of the possible topologies:

Source: [2]

Figure 2-4: Dual channel single star configuration

Source: [2]

Figure 2-5: Single channel cascaded star configuration

Figure 2-6: Dual channel cascaded star configuration

Source: [2]

Source: [2]

Figure 2-8: Dual channel hybrid example

Source: [2]

From a reliability standpoint it is no doubt preferable to use both channels as redundant media. The bus topology is the simplest option and also the cheapest making it suitable for simple applications. In this case the bus transmission line represents a weak link. In case of its severance the whole network goes out of commission due to faulty line termination.

The active star topology enables us to reduce the consequences of a failure which occurs in a part of the network. Failure of the active star element is nevertheless still a potential risk. Hybrid topologies combine the advantages of the bus and the active star. Their weaknesses can be partially made up for through a correct combination of both topologies (example Figure 2-8).

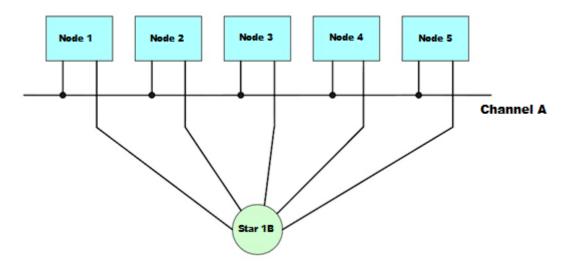

## 2.3. Link layer

This layer of the ISO/OSI model is responsible for is the equivalent of a communication controller and can be sub-divided into three sub-layers. These layers represent the core of the standard itself and provide an interface to layers below and above. These include:

- Coding/decoding layer responsible for modifying the data and physical coding of the transmitted bits.

- Protocol execution layer implements the core of the protocol, puts data into frames, controls the media.

- Controller host interface layer interface between the node and the host.

#### Figure 2-9: Physical layer and link sub-layers

Source web: http://automatizace.hw.cz/sbernice-komunikace-flexray-nejen-pro-automobily

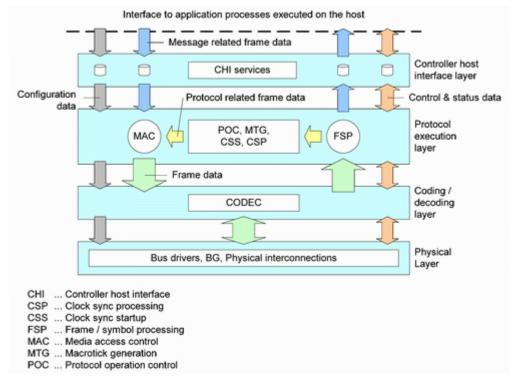

#### **2.3.1.** Architecture of a node

- Host

- > Contains the node's firmware

- > Sets the parameters of the communication controller

- > Enables/disables the usage of the bus guardian (if it is physically present)

- Communication controller

- > Implements the protocol's core

- > Provides an interface to the host

- > Generates interrupts

- > Generates the local time base macrotick (refer to section 2.4.1)

- > Synchronizes the local time base with the global time base

- > Controls access to media

- Bus driver

- > Drives and receives various bus signals

- > Detects and reports error states

- > Provides support for a remote node wakeup triggered by communication on the bus

- > Two independent channels (A and B)

- Bus Guardian

- > Provides protection against unauthorized access to the bus

- > Optional

Figure 2-10: Architecture of a FlexRay node

Source: [1]

## 2.4. Communication cycle

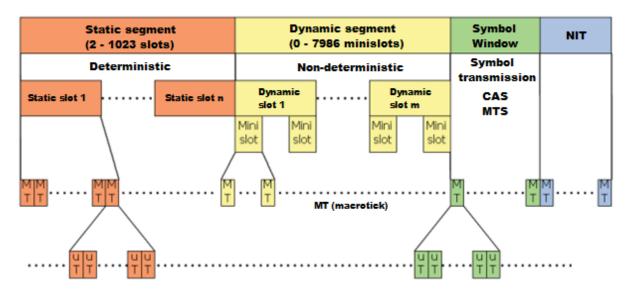

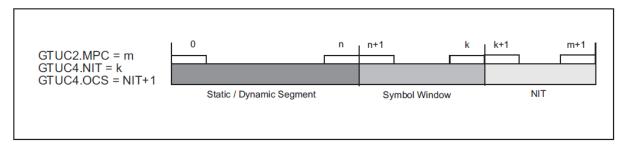

The FlexRay protocol divides time into so called communication cycles. The length of a communication cycle is parameter which needs to be determined by the network-designer. This length is constant during run-time. One communication cycle then breaks down into four different segments. These are the static segment, the dynamic segment, the symbol window and the network idle time.

Figure 2-11: Communication cycle

Source: [1]

Only the static segment and the network idle time are compulsory parts of the communication cycle. The length of the communication cycle and its division into segments must be identical in all the nodes of the cluster.

#### 2.4.1. Microtick – µT

The microtick represents the smallest and atomic time interval. It is derived from the controller's oscillator and therefore node-specific. The usual length is equal to the period of controller's time base. It is not a subject to the global clock synchronization mechanism.

#### 2.4.2. Macrotick – MT

Macrotick is a time interval identical for all the nodes in the cluster. It represents the common perception of time in the FlexRay network. A macrotick consists of an integral number of microticks, formally  $MT = \mu T \cdot k$ ;  $k \in \mathbb{N}$ , where the constant k can differ in different nodes of the cluster depending on the frequency of their time bases.

#### 2.4.3. Static segment

The communication cycle always starts with the static segment. It is a compulsory part of the communication cycle. It consists of  $n; n \in \mathbb{N}$  number of static slots. The maximum number of static slots is defined by the standard as 1024. Each slots belongs to exactly one node, however, one node can own multiple slots. The beginning and the end of a static slot is

time wise preset and cannot change at run-time according to the payload length transmitted inside the slot.

The static segment represents the deterministic part of the communication cycle and is thus suitable for the exchange of time-critical data. The guaranteed latency, however, comes at the cost of lower utilization of the communication channel.

#### 2.4.4. Dynamic segment

The dynamic segment is an optional part of the communication cycle. It's made up of  $m; m \in \mathbb{N}$  dynamic slots. Each dynamic slot is then further made up of minislots the number of which varies depending on the current frame's payload length. The duration of a minislot must be the same for all nodes in the cluster and it is defined by the number of MT which it consists of. The length of a dynamic slot is therefore not constant and its beginning and end cannot be known at network design time.

The slot counter of a communication controller then, as opposed to the static segment, holds the count for the duration of frame reception or transmission so that all the nodes in the cluster share the same value of the slot counter. The length of the dynamic segment is constant, however, for every communication cycle. It is possible for this reason that a frame assigned to one of the later dynamic slots will not be transmitter and it delayed until the next cycle (the transmission would cause the frame to overstep the dynamic segment boundary). This can happen multiple times in a row.

Cluster's behavior in this respect can be influenced by the parameter pLatestTx as defined by the FlexRay standard v2.1. This parameter sets the time in minislots when a node is allowed to start transmitting at the latest in the dynamic segment. The communication controller checks before the transmission of any frame in the dynamic segment if the minislot counter has exceeded the *pLatestTx* threshold. If so, then the transmission is suspended until the next communication cycle.

The dynamic segment represents the non-deterministic part of the communication cycle. It is therefore most suitable for the exchange of time-noncritical data. Its advantage lies in the high degree of utilization of communication channel compared to the static segment. For this reason it can reach a much higher throughput.

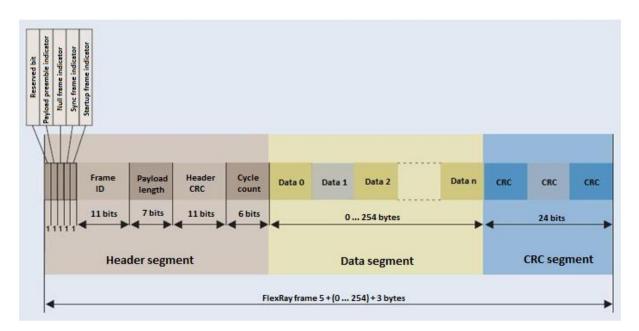

## 2.5. Frame format

A FlexRay frame is made up for three segments. First is the header segment which begins by the reserved bit and is followed by a series of indicator bits. Frame ID determines the time slot of the communication cycle in which the frame is being transmitted. It can either be a static slot or a dynamic slot but no other frames are allowed to have the same Frame ID in the same communication cycle. The payload length is indicated by a number of half-words (16 bits). The range is then from 0 to 254 bytes. The header CRC is calculated from the last two indicator bits, Frame ID and payload length. It serves as a means of verification of the transmission's correctness. The cycle count denotes the cycle number. It ranges from 0 to 63. When it reaches its maximum value it starts over from zero again. This is useful mostly for the so called cycle filtering. Nodes can for instance only transmit data every *n-th* cycle with a possible offset. In the same manner, the protocol supports also filtering of received frames. This practice, however, should not be exploited for sharing slots between nodes despite it being technically feasible.

Figure 2-12: FlexRay frame format

Source web: http://www.coleparmer.com/TechLibraryArticle/1112

The data segment contains 0 to 254 bytes of payload data. The payload length may vary in frames with the same Frame ID cycle to cycle. Therefore it's necessary to always read the payload length field. The CRC segment contains a value calculated over the entire header and data segments. The presence of two CRCs in a single frame is of the FlexRay's security features. For details on the generator polynomials and their initialization vectors for the CRC segment and the header CRC refer to the FlexRay standard (source [2]).

## 2.6. Clock synchronization

In order to enable the use of TDMA all nodes in a FlexRay cluster must have a common perception of time with a fairly high precision regardless of their individual oscillator frequencies. To accomplish this FlexRay introduces the aforementioned global time unit - macrotick. Nevertheless, real oscillators are imperfect and their frequencies fluctuate with time. Therefore, it is necessary that all nodes constantly adjust the lengths of their macroticks (Rate Correction) and the offset of individual cycles (Offset correction).

### 2.6.1. Measurement

At the beginning of each communication cycle the controller measures the time deviations between the expected reception time and the actual reception time. This is performed for every so called synchronization frame of every synchronization node (a node that transmits a synchronization frame). Measurements are done separately for both channels. The measured values for the last two cycles are stored.

|           | Even cycle              |                         | Odd cycle               |                         |

|-----------|-------------------------|-------------------------|-------------------------|-------------------------|

|           | ΔT of channel A<br>[μT] | ΔT of channel B<br>[µT] | ΔT of channel A<br>[μT] | ΔT of channel B<br>[µT] |

| Node<br>1 | 5                       | 13                      | 25                      | 32                      |

| Node<br>2 | 11                      | 10                      | 14                      | 13                      |

|           |                         |                         |                         |                         |

| Node<br>n | 35                      | 30                      | 41                      | 29                      |

#### Table 2-1: An example of measured values

#### 2.6.2. FTM algorithm

The input for the Fault Tolerant Midpoint algorithm is a list of integral values. Those values are first sorted in descending order. Depending on the number of entries we eliminate k highest and lowest values. From the remaining values we chose the highest and the lowest ones. Their arithmetical mean is the output of the FTM algorithm.

| Number of entries | k |

|-------------------|---|

| 1-2               | 0 |

| 3-7               | 1 |

| > 7               | 2 |

Table 2-2: Number of entries to eliminate

Figure 2-13: An example of FTM calculation for k = 2

Source: [2]

#### 2.6.3. Rate Correction calculation

The value of Rate Correction is calculated during the network idle time of every odd cycle from two consecutive measurements. Even cycles borrow values from their previous odd cycles. First we calculate the difference of deviations for even and odd cycles separately for channels A and B. We then take their arithmetic mean. The result is a single table of values which is then used as an input for the FTM algorithm. The FTM's output is consequently a subject to the *pClusterDriftDamping* parameter (range of insensitivity). Let's denote the result of which as *g*. The final value for Rate Correction is then saturated by *min* (*g*, *pRateCorrectionOut*) where the second argument represents the maximum admissible value for Rate Correction.

The final output of RC is an integral value which denotes by how many microticks should the next communication cycle be adjusted. Positive values represent extension and negative values shortening. The change is applied to the next two consecutive cycles and is evenly distributed over macroticks so that no two consequent macroticks differ by more than one microtick.

#### 2.6.4. Offset correction calculation

The Offset Correction value is computed in each cycle. First the minimum value for each row is taken from the table of deviations. This produces a list of values as an input for the FTM algorithm. Subsequently, we denote the FTM's output as g. The resulting value is then saturated by *min* (g, *pOffsetCorrectionOut*) where the second argument represents the maximum admissible value for Offset Correction.

#### 2.7. Startup mechanism

All nodes in a FlexRay cluster need to set up a common perception of time in order to be able to stick to their scheduled time slots and be able to receive from others. The startup mechanism thus has to perform an initialization of the time base. This is done by so called coldstart nodes. To startup a FlexRay network at least two coldstart nodes are required. One of the two becomes a leading coldstart node and the other a following coldstart node.

Prior to the startup all the nodes must be in the *ready* state meaning that they already need to be configured and if required also woken up. As the startup commences all nodes enter the *coldstart-listen* state. Each node stays in this state for a random amount of time during which it listens to the communication channel. The first node to leave this state transmits its CAS (*Collision Avoidance Symbol*). By doing so it becomes the leading coldstart node. Other coldstart nodes assume the roles of following coldstart nodes.

It can occur that two nodes transmit their CAS at the same time. For this reason a leading coldstart node always transitions to the *collision resolution stage* after transmitting the CAS. During this phase the leading coldstart node transmits a startup frame in four consecutive cycles and listens for possible collisions. In case a collision occurs all nodes have to recognize this and return to the *coldstart-listen* state and the startup process is repeated while each node decreases its counter of remaining coldstart attempts. The *coldstart-listen* state may only be entered if the number of remaining coldstart attempts is greater than zero.

If there are no conflicts detected then just after two cycles are the following coldstart nodes able to determine the correctness of the time schedule by computing the time interval between the startup frames. All nodes must know the schedule beforehand. They merely verify its correctness. The other two cycles are essential to perform rate and offset corrections. Following the four cycles all other coldstart nodes proceed to transmit their startup frames. The leading coldstart node enters the *coldstart consistency check* stage in which it checks whether the frames transmitted by following coldstart nodes comply with its schedule. This

again takes four cycles. At the end of the fourth cycle, if not interrupted by consistency check errors, the cluster is successfully started and other non-coldstart nodes can join starting with the next cycle.

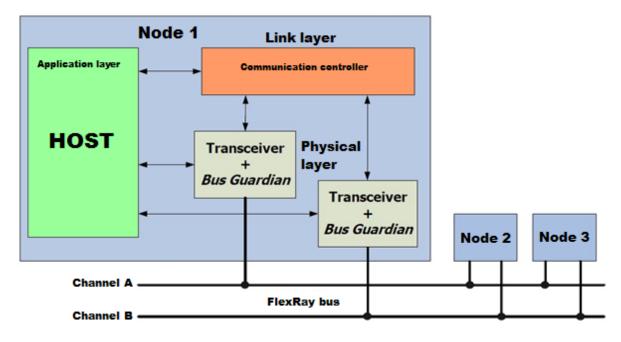

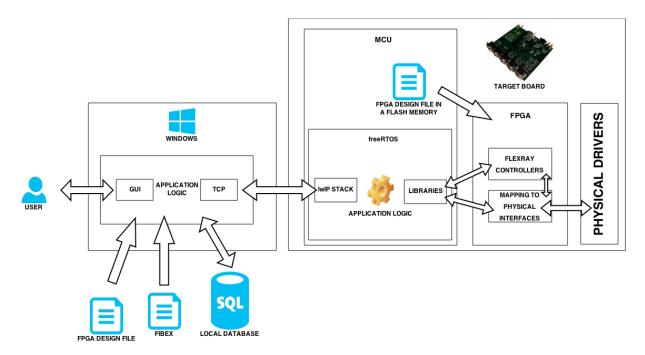

## 3. System architecture

The platform is to serve as a flexible and unique tool for monitoring and testing of vehicular networks. In its current state it is capable of monitoring FlexRay clusters by using the integrated FlexRay controller as one of the cluster's nodes. The FPGA is a key part of the system since it's responsible for the mapping of all communication outputs from the MCU to their respective drivers. But equally important are the FlexRay controllers contained within. Their number can be changed by loading a different design into the FPGA. However, the system reacts flexibly to this and reads the number from the FPGA's special register. Both the firmware and the PC application then recognize this number and provide control to the user of each controller without the need to recompile. The latest hardware version offers two physical FlexRay drivers (2 x 2 channels) to which either controller type (MCU or FPGA) can be mapped. At the time of development the mapping was static.

Figure 3-1: System architecture

All FlexRay controllers in the FPGA are capable of non-standard operations when compared to commercially available controllers. Those capabilities are aimed at the testing of the parameters of FlexRay networks. The ability to change node's parameters at runtime represents the core principal behind the tests. The MCU partakes in the tests by executing sets of commands responsible for coordinating the tests and reading the results. FlexRay controllers in the FPGA are taken from source [14] and stand as a key component which this thesis integrates into a complex testing system.

Apart from FlexRay the target board is also equipped with CAN and LIN drivers. Their utilization is not within the scope of this thesis but they are ready for future applications. Their usage can either be added to all components of the system meaning the PC application, the communication protocol and the firmware. Or they can be controlled purely from custom tasks which are described in more detail in section 5.3.

## 4. FreeRTOS

FreeRTOS is an open source real time operating system targeted at microcontrollers and small microprocessors. It has been largely successful over its 12 years of existence. A vibrant community has been formed around freeRTOS providing free professional-level support. The kernel has a very small binary image. The exact size varies depending on the components used. Despite being free freeRTOS has successfully made it into commercial applications and is known to be reliable. Such a track-record combined with the fact that a port for our chosen architecture can be easily generated with the Halcogen tool made freeRTOS a clear choice for this platform over its only considered competitor – RTEMS.

## 4.1. Port settings

The Halcogen tool from Texas Instruments offers an easy way of generating a freeRTOS port with the desired parameters. Here is a list of chosen settings:

- Tick Rate 1000 Hz, that means one tick equals one millisecond

- Minimum Stack Size 128 words

- Preemption Enabled

- Number of Priorities 3, despite only two being actually used. Wasting of processor time is prevented by tasks blocking while waiting for resources. While not being blocked tasks share processor time equally. The remaining priority is provided for possible future use.

- Heap Size 32 768 bytes, this current setting may be adjusted according to need. For instance additional heap space might be needed if a large number of user tasks were defined. More about user tasks in section 5.3.

Memory sections – are not adjustable by the Halcogen's GUI but can be considered part of port settings. However, as of now memory sections are irrelevant for this project since the memory protection unit (MPU) of freeRTOS is disabled. Though they do need to be considered if that were to change as the project expands.

### 4.2. Features used

The features of the real-time operating system that were used to build the firmware are listed in this section. These include tasks, queues and mutexes. All of these elements have to be dynamically allocated and therefore can fail to be created. It is a good practice to check the handler after allocation to see whether it has been successful. This can save a lot of time debugging for any programmer expanding the firmware with new features (such as the planned CAN and LIN).

#### 4.2.1. Tasks

A task in freeRTOS just as in any other operating system represents a small program in and of itself. There are two basic ways of creating tasks in freeRTOS depending whether we take advantage of the MPU or not. The two functions to create tasks are *xTaskCreateRestricted* and *xTaskCreate* respectively. Since the MPU is not utilized in this project only the latter function is used. Here is a list of tasks used in this thesis:

- **Command\_dispatcher** stack size = 128 words, function = commandDispatcher, priority = 1, parameters = none

- Mcu\_controller\_task stack size = 128 words, function = mcuStateMachineTask, priority = 1, parameters = none

- **Fpga\_controller\_task** stack size = 128 words, function = fpgaStateMachineTask, priority = 1, parameters = index of the controller, the number of these tasks is determined by the value read from the FPGA. One task for each FlexRay controller is created up to a maximum defined by the macro MAX\_FPGA\_FR\_CONTROLLERS.

- Lwip\_server\_task stack size = 2048 words, function = lwipTask, priority = 1 (later lowered to 0), parameters = none

- **Tcp\_send\_task** stack size = 128 words, function = tcpSenderTask, priority = 2, parameters = none

- User defined tasks –refer to section 5.3.

### 4.2.2. Queues

Queues are a means of passing data between tasks and can also serve as a way of synchronization since queues in freeRTOS are capable of blocking for a certain period of time or indefinitely. When inserting data into a queue or when retrieving it the data is always copied. Therefore, special care must be taken when dealing with large data structures. In such a situation it is advised to design the program's architecture in such a way that only pointers are stored in the queue. This approach is not used in scope of this project because the largest queued data structure is 263 bytes long and it happens very sparsely. This size has been chosen because it is required to accommodate data of largest possible FleRay payload (254 bytes). However, most commands are much shorter than that so only the required number of bytes is copied. Here is a list of used queues:

- **commandQueue** element size = 263 bytes, number of elements = 3

- **mcuFrControllerQueue** element size = 263 bytes, number of elements = 2

- **fpgaFrControllerQueue** element size = 263 bytes, number of elements = 2, the number of these tasks is determined by the value read from the FPGA. One task for each FlexRay controller is created up to a maximum defined by the macro MAX\_FPGA\_FR\_CONTROLLERS.

- **tcpSendQueue** element size = 2 bytes, number of elements =1

### 4.2.3. Mutexes, semaphores and binary semaphores

Mutexes, semaphores and binary semaphores in freeRTOS all use the same handler type *xSemaphoreHandle*. The way to distinguish them is through the method called to initialize them. Mutex is a binary semaphore that employs the priority inheritance mechanism. Mutexes are suitable for mutual exclusion. Semaphores and binary semaphores are very similar to mutexes but they do not include priority inheritance. Binary semaphores can same as mutexes only be either taken or free (not-taken, unlocked, etc.). A regular (counting) semaphore contains a counter which determines how many times it can be taken without releasing it. Both semaphore types are best suited for synchronization. Mutex named **tcpSendProtection** is used in the firmware. It is created as the binary semaphore type and is responsible for the synchronization of requests to send data from multiple state machines (both MCU and FR). Specifically, it protects the access to the TX buffer which is shared by all tasks. The mutex is released as soon as the data is written to the EMAC buffers.

## 5. Firmware

## 5.1. Porting of the lwIP stack

In order to build a protocol based on TCP between the PC application and the MCU an IP stack needs to be ported for the combination of the architecture and the real-time operating system. This can be done in many ways. For example one of the decisions that need to be made is what kind of API we want to use. LwIP offers three layers from which we can choose.

- BSD socket API the primary advantage is its portability to other stacks. It is sequential which means that it requires threading to operate it. One thread uses the API and the second thread runs the stack itself (takes care of timers, incoming packets etc.)

- Netconn API not portable to other stacks, sequential

- Raw API not portable to other stacks, uses callbacks, best performance since it doesn't have to deal with thread switching

First two options are more complicated to implement and require a deeper knowledge of the lwIP stack. Also, issues with performance might arise if more user tasks were defined. Since the porting of the lwIP stack is not the objective of this thesis but only means to an end a decision has been made to use the raw API.

## 5.2. Command processing

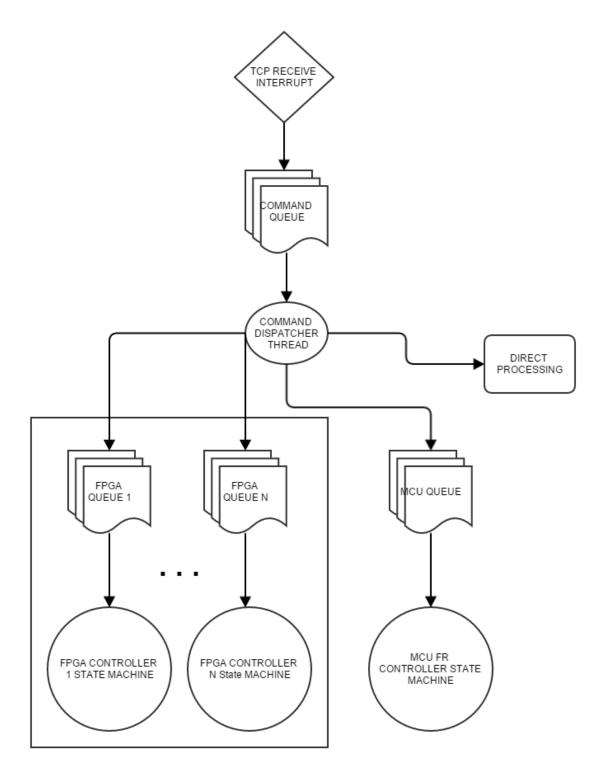

Figure 5-1 depicts the flow of command processing in the MCU. Whenever a TCP packet is received a callback function is invoked. The callback does not interpret the data. Its only job is to copy the received data into the command queue and signal the reception of data to the lwIP stack.

Considering the frequency of incoming commands it is not expected that there should be more than one element in the queue at any time. However, the queue is set to a capacity of three to allow for extreme cases.

Data from the command queue is read by the **Command\_dispatcher** task. It is set to wait indefinitely so it doesn't waste any processing time when there is no command to be processed. Upon successful retrieval of a command from the queue the dispatcher reads the command type coded in the first byte. Depending on the command type it has three options. It

can process the command itself, pass it to the Mcu\_controller\_task or pass to one of the Fpga\_controller\_tasks identified by the index in the second byte.

Figure 5-1: Command dispatching

Commands that do not belong to any FlexRay controllers are processed immediately by the dispatcher. For example when the PC application requests the number of FlexRay controllers in the FPGA. This information is has already been stored during initialization so the dispatcher simply replies with the value. Another example would be the request for the list of available user tasks.

## 5.3. Task declaration macros

One of the required features is the possibility for a programmer to define arbitrary tasks and to be able to run or suspend these tasks from the PC application. To make the definition of user tasks easier a macro has been written which serves as a sort of a task declaration API which wraps the freeRTOS task declaration API with additional code. This way the programmer doesn't need to understand exactly how the management of user tasks is implemented.

To declare a user task the programmer has to look for a section bounded by /\*----USER TASK DECLARATION----\*/ and /\*----END OF USER TASK DECLARATION----\*/. All the user tasks are supposed to be declared within this area using the following macro:

#### DECLARE\_TASK\_MANAGER\_TASK( function, name, stack, params, priority, handle )

The passed arguments are:

- **Function** a pointer to a function which the task is going to perform. The function must never exit.

- Name const char \* const type variable that is going to be displayed in the PC application as the name of the task. The programmer must avoid using the '|' character in the name since it is used as a separation character in the communication protocol.

- **Stack** A value that represents the size of the stack in words that the operating system has to allocate for the task.

- **Params** parameters that will be passed to the task

- **Priority of the task** it is recommended to use 1 but if a higher number is chosen, the programmer needs to make sure that the task either blocks or yields often enough not to starve other tasks.

- **Handle** here the programmer has to put in taskManager[x] where x is the index to the taskManager array. This value should be ascending for every declared task going from 0 to SIZE\_OF\_TASK\_MANAGER 1.

Here is an example of a correct user task declaration area:

```

uint32 ledTimeOne = 1000;

uint32 ledTimeTwo = 3000;

uint32 sciTime = 2000;

uint32 stack = configMINIMAL_STACK_SIZE;

...

/*----USER TASK DECLARATION----*/

DECLARE_TASK_MANAGER_TASK( ledTask, "led_flash_one", stack, ledTimeOne, 1,

taskManager[0] )

DECLARE_TASK_MANAGER_TASK( ledTask, "led_flash_two", stack, ledTimeTwo, 1,

taskManager[1] )

DECLARE_TASK_MANAGER_TASK( consoleTask, "console_task", stack, sciTime, 1,

taskManager[2] )

/*----END OF USER TASK DECLARATION----*/

```

When passing parameters to tasks it is the programmer's responsibility to cast them correctly in the task function since they are always being passed as pointers to the void type.

### 5.4. TCP server implementation

The server part of the system is implemented in the MCU. Upon power up or reset the MCU initializes all necessary peripherals. This happens before starting the scheduler in all cases except the EMAC. The initialization of EMAC and the lwIP stack is performed by the **Lwip\_server\_task** before entering the endless loop every freeRTOS task is required to have. The last function called by this task is **server\_init** which allocates the **struct** tcp\_pcb variable. After that it lowers its own priority to that of the idle task and enters an infinite loop. Packet reception is then handled through callbacks.

It is done this way because all the components of the lwip used in this project are designed to pass around a pointer to the pcb. The pcb variable needs to be kept valid, which means we cannot allow the stack space to be freed. It would require a lot of extra time and effort to rewrite the lwip which also invites a number of potential errors.

Packet transmission is handled by a special task (*tcpSenderTask*). Whenever a task wants to send data over the TCP it has to acquire the *tcpSendProtection* mutex which protects access to the TX buffer. After writing the data into the buffer the task has to enqueue the data length into *tcpSendQueue*. This causes the *tcpSenderTask* to immediately preempt any other running task since it has the highest priority. And it writes the requested amount of data into the EMAC buffers. Consequently, it releases the *tcpSendProtection* mutex. The queue can

only hold one element at a time. There is no point making this queue any bigger because no other task can acquire the *tcpSendProtection* mutex until the *tcpSenderTask* releases it.

# 5.5. EMIF

The External Memory Interface (EMIF) is a controller integrated in the TMS570LS3137ZWT chip. The purpose of EMIF is to provide a means for the MCU's core to connect to a variety of external devices including SDRAMs or asynchronous devices such as NOR Flash and SRAM. In case of this project it is used to interface to the FPGA's registers. The registers are mapped to CPU's address space and can be accessed simply by reading from and writing to an address using pointers. The following macros are provided to facilitate the access:

```

#define READ_CONTROLLER_VALUE(BASE, CONTROLLER_INDEX, OFFSET) \

(*((volatile unsigned int *) ((BASE) + ((CONTROLLER_INDEX)*(FPGA_FR_CONTROLLER_LENGTH)) +

(OFFSET))))

#define WRITE_CONTROLLER_VALUE(BASE, CONTROLLER_INDEX, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + ((CONTROLLER_INDEX)*(FPGA_FR_CONTROLLER_LENGTH)) +

(OFFSET))) = (VALUE))

#define READ_VALUE_8BIT(BASE, OFFSET) \

(*((volatile unsigned char *) ((BASE) + (OFFSET)))) = (VALUE))

#define WRITE_VALUE_8BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned char *) ((BASE) + (OFFSET))) = (VALUE))

#define READ_VALUE_32BIT(BASE, OFFSET) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define READ_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))))

#define WRITE_VALUE_32BIT(BASE, OFFSET, VALUE) \

(*((volatile unsigned int *) ((BASE) + (OFFSET))) = (VALUE))

```

It should be noted that tasks in freeRTOS normally only allow access to their own stack and to the heap. Other memory regions are accessible according to the setting of MPU regions. The MPU is not needed in this project so it is left uninitialized. Otherwise either the memory region access right would have to be changed or a special restricted type of task would have to be used instead (using *xTaskCreateRestricted*). Restricted tasks are an unnecessary over complication. Leaving the MPU off allows for the use of regular tasks even when accessing the EMIF memory regions.

Communication constants of the EMIF controller have to be set in mutual compliance with the FPGA's EMIF module. It is configured for asynchronous access. Here are the parameters used:

| - EMIF: ASYNC1 Config - |        |                      |

|-------------------------|--------|----------------------|

| Select Strobe Mode      |        | Page Mode            |

| NOR Flash               |        | Page Delay: 0 Cycles |

| Extended Wait           |        | Page Size: 4_words   |

| - EMIF: ASYNC1 Timings  |        |                      |

| W_SETUP: 1              | Cycles | ASIZE: 16_bit -      |

| W_STROBE: 10            | Cycles | ASYNC1 WAIT pin0 -   |

| W_HOLD: 1               | Cycles |                      |

| R_SETUP: 1              | Cycles |                      |

| R_STROBE: 9             | Cycles |                      |

| R_HOLD: 1               | Cycles |                      |

| TA: 1                   | Cycles |                      |

|                         |        |                      |

Figure 5-2: EMIF Settings

## 5.6. MCU state machines

All state machines in the MCU are event-driven. That means they can only perform actions on edges i.e. while receiving a command.

### 5.6.1. MCU Connection state machine

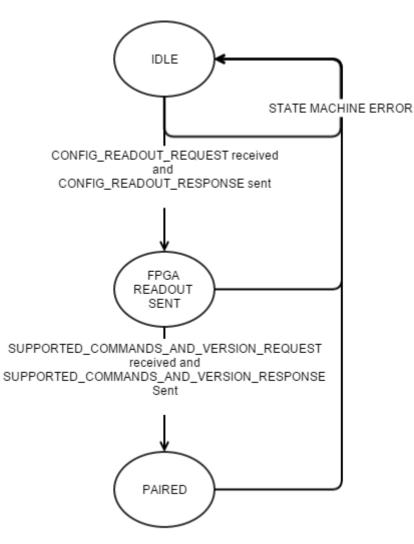

This state machine is the simplest in the MCU. Its only purpose is to track the connection state of the protocol. The state of the connection has three phases. First one is IDLE, which is the initial state. Upon receiving a request for the number of FlexRay controllers in the FPGA the dispatcher task sends the response and transitions to the FPGA\_READOUT\_SENT state. Here it remains until the PC application requests the firmware version together with a list of supported commands. It then sends the needed answer and finally transitions to the PAIRED state. At this point it is allowed to pass commands to their respective FlexRay state machines.

Figure 5-3: MCU Connection state machine

## 5.6.2. MCU FR state machine

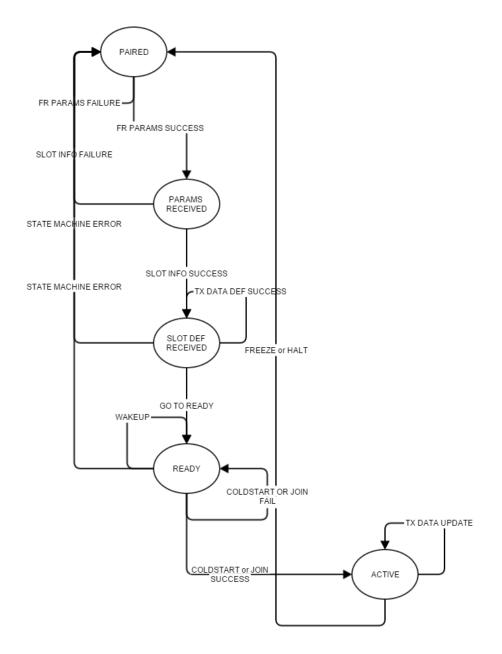

Figure 5-4: State machine for handling the MCU's FlexRay controller

State machine depicted in Figure 5-4 is responsible for implementing the parts of the communication protocol that concern the FlexRay controller in the MCU. It starts with the PAIRED state which is where the connection state machine left off and started passing commands to FlexRay state machines. The states can be divided into two phases - configuration and operation. Configuration includes the PAIRED, PARAMS\_RECEIVED and SLOT\_DEF\_RECEIVED states. Upon receiving the following constants:

- *pKeySlotusedForStartup*

- *pKeySlotUsedForSync*

- gColdStartAttempts

- pAllowPassiveToActive

- pWakeupChannel

- pSingleSlotEnabled

- pAllowHaltDueToClock

- pChannels

- pdListenTimeOut

- gListenNoise

- gMaxWithoutClockCorrectionPassive

- gMaxWithoutClockCorrectionFatal

- gNetworkManagementVectorLength

- gdTSSTransmitter

- gdCASRxLowMax

- gdSampleClockPeriod

- pSamplesPerMicrotick

- gdWakeupSymbolRxWindow

- pWakeupPattern

- gdWakeupSymbolRxIdle

- gdWakeupSymbolRxLow

- gdWakeupSymbolTxIdle

- gdWakeupSymbolTxLow

- gPayloadLengthStatic

- *pLatestTx*

- pMicroPerCycle

- gMacroPerCycle

- gSyncNodeMax

- pMicroInitialOffset[A]

- pMicroInitialOffset[B]

- pMacroInitialOffset[A]

- pMacroInitialOffset[B]

- gdNIT

- gOffsetCorrectionStart

- pDelayCompensation[A]

- *pDelayCompensation[B]*

- *pClusterDriftDamping*

- pDecodingCorrection

- pdAcceptedStartupRange

- pdMaxDrift

- gdStaticSlot

- gNumberOfStaticSlots

- gdMinislot

- gNumberOfMinislots

- gdActionPointOffset

- gdMinislotActionPointOffset

- gdDynamicSlotIdlePhase

- pOffsetCorrectionOut

- pRateCorrectionOut

- *pExternOffsetCorrection*

- *pExternRateCorrectio*

Along with additional information about channel usage, startup and synchronization the state machine writes them into the FlexRay controller. Subsequently, the state advances to PARAMS\_RECEIVED. In this state the information about RX and TX frames is expected. The order of buffers is important. RX frames go first and TX frames second. This is necessary to make the firmware much simpler and more elegant. This information is stored and the firmware uses it to calculate pointers to the FlexRay message RAM for all the message buffers. RX buffers are configured right away since they don't require any payload data. Afterwards, the machine shifts to the SLOT\_DEF\_RECEIVED state. Here it receives the data that is to be transmitted out of the TX buffers. The order of the buffers has to follow the same order in which the frames were defined in the previous stage. For example if the following four frames were defined:

- slotID = 12, RX

- slotID = 2, RX

- slotID 5, TX

- slotID 23, TX

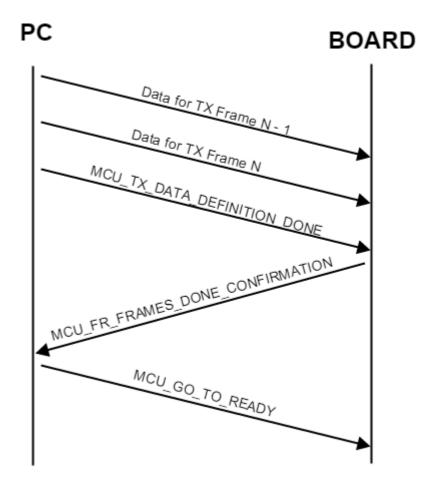

Then the first TX data must be for the frame transmitted in slot 5 and the second in slot 23. At the end of data definition a double acknowledge mechanism is used. See Figure 5-5 for better descriptiveness.

Figure 5-5: Details of message exchange at the end of data definition

When the MCU receives the MCU\_GO\_TO\_READY command it can finally transition to the READY state. Now, the FlexRay controller can optionally perform a cluster wakeup. Other than that, it waits until it is instructed to either coldstart or to join a running network. The startup procedure may fail. The result is reported to the PC application. In case of success the controller now finds itself in the ACTIVE state. In case of failure it remains in the READY state. Then a new startup command may be issued by the PC application. Details about the message format can be found in section 7.4.

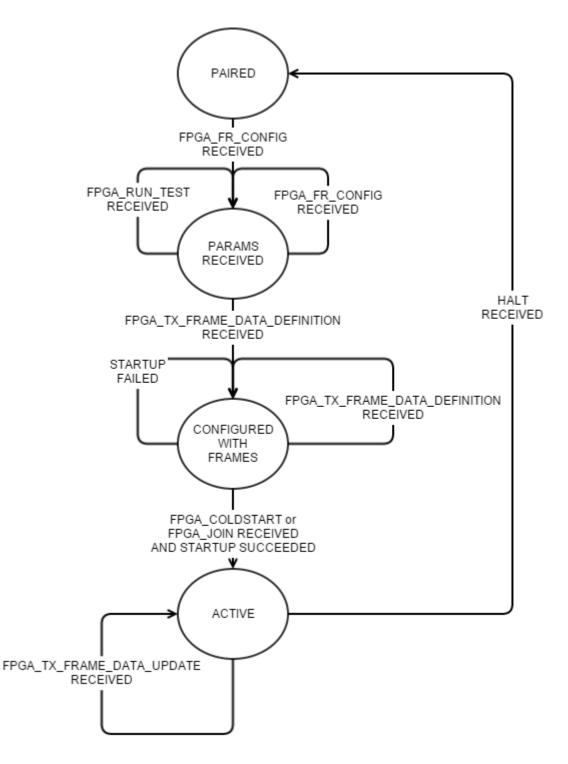

## 5.6.3. FPGA FR state machine

Figure 5-6: MCU FPGA State machine

Each **Fpga\_controller\_task** (section 4.2.1) manages a state machine shown in Figure 5-6. In addition to what can be seen in the figure each state also has an edge to the PAIRED

state as a reaction an internal reset command which is issued every time a new configuration is loaded into the FPGA. With the exception of this internal command the state machine takes action exclusively in reaction to commands passed to it by the command dispatcher. When an action is finished the task blocks on its receive queue waiting for a new command. This way it doesn't consume any CPU time when it's not needed.

First the state machine expects cluster and node parameters in the format which is detailed in section 7.4. After receiving the first definition of a TX frame it transitions to the CONFIGURED WITH FRAMES state. Other TX frames sent by the client are processed in this state. However, there is a limit to the number of TX frames that can be defined in a single FPGA FlexRay controller. The current number is 4. This constant can be adjusted in the VHDL code of the controller. If the client tries to define more frames than that the state machine responds with an error message.

The PARAMS RECEIVED state is intended for the future implementation of running tests. Configuring TX or RX buffers is usually included in the tests themselves. Only FlexRay parameters need to be set. That is why PARAMS RECEIVED is the correct launching state and not CONFIGURED WITH FRAMES.

# 6. PC Application

# 6.1. State machines

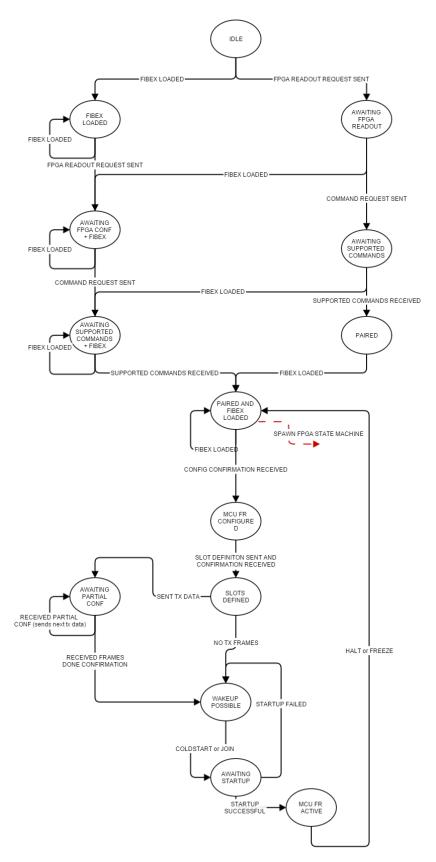

Just like in the case of MCU the state machines in the PC application are edge oriented. Only, in this case, they can react not only to received frames over TCP but also to user interactions. In addition to what can be seen in the figures, each state possesses an edge to the IDLE state in case of an unexpected action (state machine error). Those edges were left out to keep the graphs neatly arranged.

The PC application manages only two state machines. The first one is solely responsible for managing the connection to the board, keeping track whether the fibex file has been loaded and the MCU's FlexRay controller itself. It also spawns the instances of state machines responsible for the FPGA controllers. The decision to merge all these functions into one state machine has been made for several reasons:

- It saves lines of code

- It avoids having to coordinate more state machines with one another

- It makes it clearer (which might of course be subjective)

So the state machine contains all the functionality that could reasonably possible be fit in. However, it was not feasible to include the FPGA state machines since there are multiple instances of those and the number of them is not known beforehand. And even if it were the resulting states would be a Cartesian product of all the states starting at a certain point. This would unacceptably inflate the number of states.

## 6.1.1. General state machine

At the beginning the state machine splits into two branches (see Figure 6-1). One of them is where the fibex file is loaded before connecting to the board and the other one after. A fibex file is a compulsory input for this application. It has been chosen as the standard way of describing FlexRay networks in the industry. However, the user is still allowed to edit the parameters even after loading the fibex. This gives the user freedom to experiment without having to edit the fibex file itself but it can also compromise the ability of controllers to integrate into a cluster. There is no mechanism in place which would check whether the new parameters are still compatible with the originally loaded fibex. A user with at least basic knowledge of the FlexRay standard is assumed.

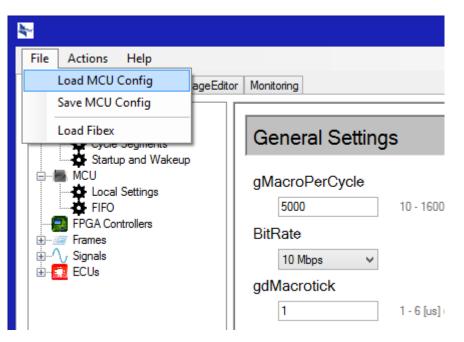

Figure 6-1: PC application's main state machine

Once the machine reaches the PAIRED or the PAIRED AND FIBEX LOADED state the "FPGA Status" window (see 6.2.5) can be opened. This spawns one FPGA state machine (see 6.1.2) for each controller in the FPGA. These state machines are managed through the UI of this window.

Next comes the configuration phase which practically mirrors the state machine in 5.6.2. The MCU\_FR\_CONFIGURED state is entered once a confirmation from the MCU is received that setting of the cluster constants is finished. Without any user interaction the state machine then proceeds to send details about monitored frames followed by frames added in the Message Editor tab. As mentioned previously, the order of frames matters! Then again without any user interaction, provided no errors were detected, the state machine starts sending data for the TX frames defined in the previous step (in the same order). This data is stored in their corresponding message buffers in the FlexRay controller and will be scheduled for transmission as soon as the node comes online. For the double acknowledgement mechanism which follows this data exchange refer back to Figure 5-5.

Now the UI enables the user to perform a wakeup of the cluster or select one of the startup options. After sending a command to perform a coldstart or to integrate itself to a running network the application waits for a confirmation from the MCU that the startup was successful. Monitoring is automatically triggered in case of successful startup. Issuing a halt or freeze command will set it back to PAIRED\_AND\_FIBEX\_LOADED state and a new configuration can be used. If the startup fails the state machine transitions back to WAKEUP\_POSSIBLE and the user can repeat the attempt.

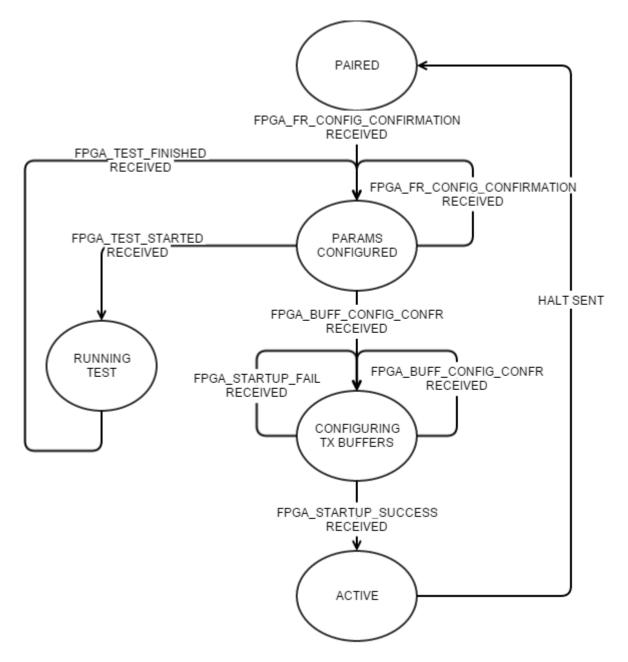

## 6.1.2. FPGA State Machine

Figure 6-2: PC FPGA State machine

This state machine is practically a mirror copy to its MCU counterpart (see Figure 5-6). It has a separate state for testing since it's not in charge of the test's execution and has to wait for the server to report that the test is finished. In the meantime the state machine is not allowed to do anything else. State transition with the exception of sending a halt command is in all cases driven by receiving a confirmation for a successful transition on the server side.

## 6.2. Features

#### 6.2.1. Monitoring and frame transmission

The primary purpose of the platform is to monitor communication of a FlexRay bus and to be able to transmit frames of its own. In order to monitor a frame it needs to be selected as a monitored frame in the Cluster Setup tab as seen in Figure 6-3.

| Cluster Setup FPGA Tests MessageEditor                                                                                                                                           | Monitoring             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Cluster     MCU     FPGA Controllers                                                                                                                                             | Frame  Monitored       |

| Frames          Frame346_S[40]_B[0]_P[2]         Frame346_S[121]_B[3]_P[4]         Frame348_S[121]_B[1]_P[4]         Frame348_S[121]_B[1]_P[4]         Frame349_S[121]_B[0]_P[2] | Short Name<br>frame346 |

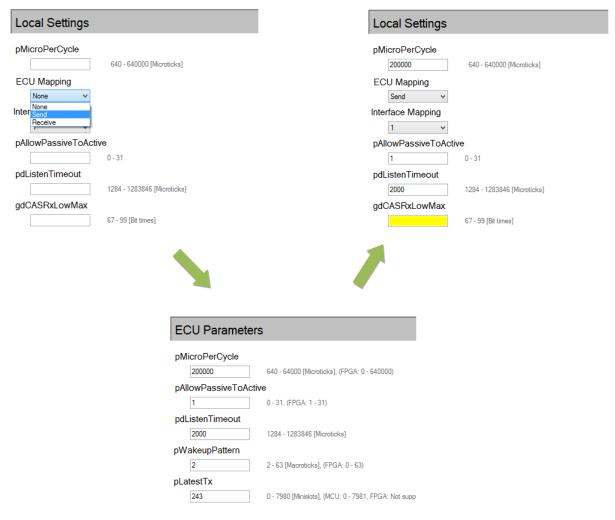

Figure 6-3: How to select a frame to be monitored

The next step is to define the outgoing communication. In the Message Editor tab the user can take advantage of the "Copy from Cluster Setup" button. In order to do that the user must first setup controller mapping. In Cluster Setup in the "MCU $\rightarrow$ Local Settings" menu choose one of the available ECUs in the "ECU Mapping" combo box. This also copies all the parameters from the ECU to the Local Settings panel. The same kind of mapping can be performed for the FPGA Controllers. Only the application must first be connected to the board (Actions $\rightarrow$ Connect to Board). This is necessary because the application must first find out how many FlexRay controllers are actually present in the FPGA. Once the mapping is done the button "Copy from Cluster Setup" will add all frames from the Cluster Setup, that belong to ECUs to which a physical controller is mapped. This way is much preferable to adding frames manually which is also supported.

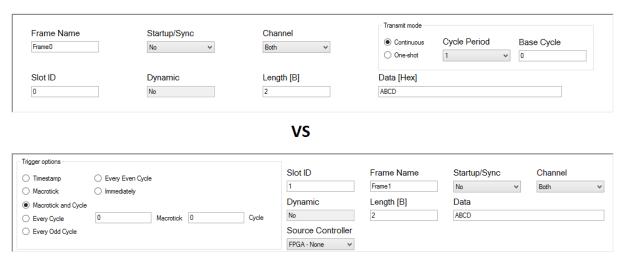

The application distinguishes between two types of frames - MCU frames and FPGA frames. The difference can be noticed when clicking on frames of both types in the Message Editor tab. It is also shown in Figure 6-4.

Figure 6-4: Difference between FPGA and MCU frames

These differences are needed due to different capabilities of said controllers to trigger frame's transmission. The FPGA controller offers more options. However, the MCU has the upper hand when it comes to periodicity. The cycle code is capable of expressing periods ranging from 1 to 64 cycles with offsets from 0 to 63. As opposed to the FPGA which can only send ever cycle or every even cycle.

An important thing to note is that if the user wants to see the frames transmitted by the MCU or one of the FPGA controllers he still needs to mark those frames as monitored. Having them in Message Editor is not enough. Figure 6-5 shows an example of the Message Editor tab with the MCU mapped to an ECU which transmits thirteen different frames and a FPGA controller which only has one frame. In order to coldstart a network one of the frames belonging to the coldstart node must be defined as "Startup & Sync". There may only be one such or "Sync" frame per node. The application takes care of this and doesn't allow the user to define more.

| Copy from Cluster S       | etup             |         |         |            | 🖶 Add a N    | Add a MCU Frame |         | + Add a FPGA Frame |      | × | X Delete Selected Frame |

|---------------------------|------------------|---------|---------|------------|--------------|-----------------|---------|--------------------|------|---|-------------------------|

| Frame Name                | Source           | Slot ID | Channel | Base Cycle | Cycle Period | Startup/Sync    | Dynamic | Length [B]         | Data |   |                         |

| frame346_S[40]_B[0]_P[2]  | MCU              |         | Both    |            |              |                 |         |                    |      |   |                         |

| rame347_S[121]_B[3]_P[4]  | MCU              | 121     | Both    | 3          | 4            | No              | Yes     | 2                  |      |   |                         |

| rame348_S[121]_B[1]_P[4]  | MCU              | 121     | Both    | 1          | 4            | No              | Yes     | 2                  |      |   |                         |

| rame349_S[121]_B[0]_P[2]  | MCU              | 121     | Both    | 0          | 2            | No              | Yes     | 2                  |      |   |                         |

| rame398_S[1]_B[0]_P[1]    | MCU              | 1       | Both    | 0          | 1            | Startup & Sync  | No      | 2                  |      |   |                         |

| rame398_S[74]_B[0]_P[1]   | MCU              | 74      | Both    | 0          | 1            | No              | No      | 2                  |      |   |                         |

| rame624_S[40]_B[1]_P[4]   | MCU              | 40      | Both    | 1          | 4            | No              | No      | 4                  |      |   |                         |

| rame1000_S[224]_B[0]_P[8] | MCU              | 224     | Both    | 0          | 8            | No              | Yes     | 9                  |      |   |                         |

| rameAB_S[13]_B[1]_P[4]    | MCU              | 13      | Both    | 1          | 4            | No              | No      | 5                  |      |   |                         |

| rameA_S[13]_B[0]_P[2]     | MCU              | 13      | Both    | 0          | 2            | No              | No      | 2                  |      |   |                         |

| rameA_S[13]_B[3]_P[4]     | MCU              | 13      | Both    | 3          | 4            | No              | No      | 2                  |      |   |                         |

| rame_25_S[2]_B[0]_P[1]    | MCU              | 2       | Both    | 0          | 1            | No              | No      | 2                  |      |   |                         |

| frame_25_S[75]_B[0]_P[1]  | MCU              | 75      | Both    | 0          | 1            | No              | No      | 2                  |      |   |                         |

| frame397_S[88]_B[0]_P[1]  | FGPA Controller1 | 88      | Both    | 0          | 1            | No              | No      | 2                  |      |   |                         |

Figure 6-5: Message Editor tab example

Monitoring is automatically activated by coldstarting a network or joining one. It can be paused and started again at any time while the cluster is running. To change data being sent, select a frame from the combo box in the bottom panel of the Monitoring tab. Now the data can be adjusted. The controller is notified of the change by clicking on the green arrow. The selection in the combo boxes is filled automatically by frames belonging to the MCU or the FPGA. In case of the MCU frames this happens as it transitions into the WAKEUP\_POSSIBLE state. As for the FPGA frames, all frames belonging to a particular FPGA controller are added to the selection when the application receives a confirmation of the "Configure Frames" action in the "FPGA Status" window. Those frames are also removed when the node leaves the active state.

| Cluster Setup | FPGA Tests M | essageEditor Mo | onitoring |               |      |         |            |                                                                  |

|---------------|--------------|-----------------|-----------|---------------|------|---------|------------|------------------------------------------------------------------|

| O Pa          | ause         | Absolute time   | ×         | Delete record |      |         |            | Save                                                             |

| Time [ms]     | Cycle        | Slot ID         | Channel   | Startup       | Sync | Dynamic | Length [B] | Data                                                             |

| 2             |              |                 |           |               |      |         |            | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 3             | 0            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 13            | 1            | 9               | А         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 13            | 1            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 31            | 2            | 9               | Α         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 31            | 2            | 8               | Α         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 50            | 3            | 9               | А         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 50            | 3            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 62            | 4            | 9               | А         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 62            | 4            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 80            | 5            | 9               | А         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 80            | 5            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 92            | 6            | 9               | Α         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 92            | 6            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 110           | 7            | 9               | A         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 110           | 7            | 8               | А         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |

| 122           | 8            | 9               | А         | Yes           | Yes  | No      | 32         | d769a090d9881b0d8166a637c3437200c0f72f77c002e4ede0f7254b6cec5225 |

| 122           | 8            | 8               | A         | Yes           | Yes  | No      | 32         | f34e50adfefc2a8a00c2b657d44669fcce067c7a3edebf94457c1209076e3ff7 |