CZECH TECHNICAL UNIVERSITY IN PRAGUE

**Faculty of Electrical Engineering**

**Master's Thesis**

# **Graphical CPU Simulator with Cache Visualization**

Karel Kočí

May 2018

## ZADÁNÍ DIPLOMOVÉ PRÁCE

#### I. OSOBNÍ A STUDIJNÍ ÚDAJE

| Příjmení:                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                    |                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| i injineni.                                                                                                                                                                                                                  | Kočí                                                                                                                                                                                                                                               | Jméno: Karel                                                                                                                                                                                                                                                       | Osobní číslo: 406446                                                           |

| Fakulta/ústav:                                                                                                                                                                                                               | Fakulta elekt                                                                                                                                                                                                                                      | rotechnická                                                                                                                                                                                                                                                        |                                                                                |

| Zadávající kate                                                                                                                                                                                                              | edra/ústav: Kate                                                                                                                                                                                                                                   | edra řídicí techniky                                                                                                                                                                                                                                               |                                                                                |

| Studijní progra                                                                                                                                                                                                              | m: Kybernetika a                                                                                                                                                                                                                                   | a robotika                                                                                                                                                                                                                                                         |                                                                                |

| Studijní obor:                                                                                                                                                                                                               | Systémy a říz                                                                                                                                                                                                                                      | zení                                                                                                                                                                                                                                                               |                                                                                |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                    |                                                                                |

| UDAJE K DIP                                                                                                                                                                                                                  | Lomové prá                                                                                                                                                                                                                                         | ACI                                                                                                                                                                                                                                                                |                                                                                |

| Název diplomové                                                                                                                                                                                                              | práce:                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                    |                                                                                |

| Grafický simulá                                                                                                                                                                                                              | tor činnosti prod                                                                                                                                                                                                                                  | cesoru a činnosti vyrovnávací paměti                                                                                                                                                                                                                               |                                                                                |

| Název diplomové                                                                                                                                                                                                              | práce anglicky:                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                    |                                                                                |

| Graphical CPU                                                                                                                                                                                                                | Simulator with C                                                                                                                                                                                                                                   | ache Visualization                                                                                                                                                                                                                                                 |                                                                                |

| Pokyny pro vypra                                                                                                                                                                                                             | cování:                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                    |                                                                                |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                    | IPS s grafickou reprezentací procesoru a pln                                                                                                                                                                                                                       |                                                                                |

| ,<br>zřetězeném s bez                                                                                                                                                                                                        | a s řešením hazard                                                                                                                                                                                                                                 | ormátu ELF. Procesor by mel umožňovat prá<br>ních stavů.<br>ve zdrojové podobě.                                                                                                                                                                                    | áci ve třech režimech: jedno-cyklovém                                          |

| zřetězeném s bez                                                                                                                                                                                                             | a s řešením hazard<br>entujte a publikujte v                                                                                                                                                                                                       | ních stavů.                                                                                                                                                                                                                                                        | ici ve třech režimech: jedno-cyklovém                                          |

| z <sup>ř</sup> etězeném s bez<br>4. Projekt zdokum<br>Seznam doporučá<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats                                                                                        | a s řešením hazard<br>entujte a publikujte<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 012374                                                                                                                                        | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir                                                                                                                            | Hardware/Software Interface, 4rd ed.                                           |

| zřetězeném s bez<br>4. Projekt zdokum<br>Seznam doporučí<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats<br>education 10.114                                                                                 | a s řešením hazard<br>entujte a publikujte<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 012374<br>. (2002). Mipslt: a s                                                                                                               | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir<br>9.                                                                                                                      | Hardware/Software Interface, 4rd ed.                                           |

| zřetězeném s bez<br>4. Projekt zdokumo<br>Seznam doporučk<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats<br>education 10.114<br>Jméno a pracoviš                                                            | a s řešením hazard<br>entujte a publikujte<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 01237.<br>. (2002). Mipslt: a si<br>I5/1275462.127547<br>tě vedoucí(ho) dip                                                                   | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir<br>9.                                                                                                                      | Hardware/Software Interface, 4rd ed.                                           |

| zřetězeném s bez<br>4. Projekt zdokumo<br>Seznam doporučkí<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats<br>education 10.114<br>Jméno a pracoviš<br>Ing. Pavel Píša,                                       | a s řešením hazard<br>entujte a publikujte v<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 012374<br>(2002). Mipslt: a s<br>45/1275462.127547<br>tě vedoucí(ho) dip<br><b>Ph.D., katedra</b>                                           | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir<br>9.<br>plomové práce:                                                                                                    | Hardware/Software Interface, 4rd ed.                                           |

| zřetězeném s bez<br>4. Projekt zdokumo<br>Seznam doporuča<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats<br>education 10.114<br>Jméno a pracoviš<br>Ing. Pavel Píša,<br>Jméno a pracoviš<br>Datum zadání di | a s řešením hazard<br>entujte a publikujte v<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 012374<br>(2002). Mipslt: a si<br>45/1275462.127547<br>tě vedoucí(ho) dip<br><b>Ph.D., katedra</b><br>tě druhé(ho) vedo<br>plomové práce: 2 | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir<br>9.<br>plomové práce:<br>řídicí techniky FEL<br>bucí(ho) nebo konzultanta(ky) diplomové<br>26.09.2017 Termín odevzdání o | Hardware/Software Interface, 4rd ed.                                           |

| zřetězeném s bez<br>4. Projekt zdokumo<br>Seznam doporuča<br>[1] Patterson, D. A<br>Morgan Kaufman,<br>[2] Brorsson, Mats<br>education 10.114<br>Jméno a pracoviš<br>Ing. Pavel Píša,<br>Jméno a pracoviš<br>Datum zadání di | a s řešením hazard<br>entujte a publikujte<br>ené literatury:<br>., and J. L. Henness<br>2011. ISBN: 01237.<br>. (2002). Mipslt: a si<br>15/1275462.127547<br>tě vedoucí(ho) dig<br><b>Ph.D., katedra</b><br>tě druhé(ho) vedo                     | ních stavů.<br>ve zdrojové podobě.<br>sy. Computer Organization and Design: The<br>47503.<br>imulation and development environment usir<br>9.<br>plomové práce:<br>řídicí techniky FEL<br>bucí(ho) nebo konzultanta(ky) diplomové<br>26.09.2017 Termín odevzdání o | Hardware/Software Interface, 4rd ed.<br>ng animation for computer architecture |

CVUT-CZ-ZDP-2015.1

© ČVUT v Praze, Design: ČVUT v Praze, VIC

## / Declaration

I declare that this thesis has been composed solely by myself and that it has not been submitted, in whole or in part, in any previous application for a degree. Except where states otherwise by reference or acknowledgment, the work presented is entirely my own.

In Prague 25.5.2018

\_\_\_\_\_

## Abstrakt / Abstract

V předmětu Architektura Počítačů vyučovaném na Českém Vysokém Učení Technickém v Praze, Fakultě Elektrotechnické se v tuto chvíli používá starý emulátor MIPS procesory MipsIt. Ten poskytuje vlastnosti důležité pro nahlédnutí do vnitřního fungování procesoru. I přesto, že byl emulátor distribuován se světově uznávanou učebnicí a dané téma tak aplikace samotná je již zastaralá. Podporuje pouze Windows a nejsou k ní zdrojové kódy. Cílem této práce je vytvořit vlastnostmi srovnatelnou náhradu založenou na aktuálních softwarových technologiích.

#### An old MipsIt emulator of MIPS processor is used as educational processor model in Computer Architectures course taught on Czech Technical University in Prague, Faculty of Electrical Engineering currently. It provides features important for student insight into the inner working of a processor. Even that the emulator has been distributed with world recognized textbook on the topic, the application is already archaic, Windows only and without source code. A goal of this thesis is to provide features equivalent replacement based on current software technologies.

## **Contents** /

| 1 In | troduction1                                        |

|------|----------------------------------------------------|

| 2 M  | IPS Instruction Set Architec-                      |

| tu   | ire2                                               |

| 2.1  | Data Formats2                                      |

|      | Registers3                                         |

| 2.3  | Instruction Formats and In-                        |

|      | structions Description3                            |

|      | 2.3.1 Arithmetic Instructions4                     |

|      | 2.3.2 Logical Instructions5                        |

|      | 2.3.3 Shift Instructions5                          |

|      | 2.3.4 Branch and Jump In-                          |

|      | structions                                         |

|      | 2.3.5 Load and Store In-                           |

|      | structions                                         |

|      | 2.3.6 Move Instructions                            |

| 0.4  | 2.3.7 Pseudo Instructions                          |

|      | Pipeline Architecture7<br>Load/Store Architecture9 |

| 2.0  | 2.5.1 Cache                                        |

| 3 E4 | eatures Required for Educa-                        |

|      | on                                                 |

|      | Tutorial Illustrating Basic                        |

| 0.1  | CPU Structure                                      |

| 3.2  | Memory Access and cache                            |

|      | Usage Tutorial 13                                  |

| 3.3  | Pipelines and Hazards Tuto-                        |

|      | rial 14                                            |

| 3.4  | Memory Mapped I/O Tuto-                            |

|      | rial 14                                            |

|      | kisting MIPS simulators $\dots \dots 15$           |

|      | MipsIt                                             |

|      | QtSpim                                             |

|      | Mars                                               |

|      | WeMips                                             |

| 4.5  | MIPS Simulator (mipssimu-                          |

| 16   | lator) 21<br>Qemu 22                               |

|      | Hardware Description Based                         |

| 4.1  | simulation                                         |

| 5 M  | <b>IPS Simulator Design</b>                        |

|      | Simulator Configuration 24                         |

|      | Registers Simulation                               |

|      | Memory Simulation                                  |

| -    | 5.3.1 Cache Implementation 27                      |

| 5.4  | Instruction Decoding                               |

|      | Instructions Execution                             |

| 5.5.1 Hazard Unit                  | 28 |

|------------------------------------|----|

| 5.6 Program Loading                | 29 |

| 5.7 Decoding to Instruction        |    |

| Mnemonic                           | 29 |

| 6 MIPS simulator Graphics Design . | 30 |

| 6.1 Simulator Configuration Di-    |    |

| alog                               | 30 |

| 6.2 Main Simulator Window          | 32 |

| 6.3 CPU Scheme View                | 33 |

| 6.3.1 Scheme Blocks                | 36 |

| 6.3.2 Signals and Buses            | 36 |

| 6.4 Registers View                 | 37 |

| 6.5 Program and Data Memory        |    |

| View                               | 38 |

| 6.6 Program and Data Cache         |    |

| View                               | 39 |

| 7 Conclusion                       | 42 |

| References                         | 43 |

| A Glossary                         | 45 |

| B Content of attached CD           | 46 |

## Tables /

| 2.1. | MIPS instructions binary for- |

|------|-------------------------------|

|      | mat4                          |

| 2.2. | Hazard resolve map9           |

# Chapter **1** Introduction

Computers are dominating a lot of industry sectors, including engineering as they are essential production tools. At least basic knowledge of the inner working of a processor and ability to predict its influence on performance, security and safety consequences is important for each programmer expert, computer, processor and embedded systems designer and advanced user. That is why the Computer Architectures course is included in electronics, informatics and robotic specializations at Faculty of Electrical Engineering of Czech Technical University same as at all similar world recognized technical universities. MIPS<sup>1</sup> architecture is selected as basic demonstration model because its first implementation can be easily understood and implemented as connection of basic blocks.

MIPS simulator MipsIt is used for practical parts of Computer Architectures course. Unfortunately this simulator is getting old and its usage becomes problematic. Crashes are common and some functionality such as simulation restart randomly breaks and requires program restart. Updating currently used program is not possible because source code is not freely available. Because of that the goal of this thesis is to implement replacement simulator.

Simulator implemented as part of this thesis is implemented in C++ programing language using Qt toolkit. It's called QtMips. It is supposed to present graphical user interface (GUI) with visualization of microprocessor interworking. Both pipelined and single-cycle CPU are implemented implemented and visualized.

Simulator is also expected to implement cache subsystem with variable size.

Programs to simulator should be loaded in Executable and Linkable file format (ELF). This format is considered as a standard for executables, because it is default output from compilers such as GNU C Compiler (GCC).

The thesis starts with an analysis of MIPS processor design, instruction set, and possible implementations. That is followed by section looking into features required for education. Next section evaluates possibility to use existing simulators instead of MipsIt or as a base for new implementation. It is followed by two chapters describing simulator technical and graphical design.

$<sup>^1~\</sup>mathrm{MIPS}$  is a cronym originating from initial goal to design microprocessor without interlocked pipeline stages.

# Chapter **2** MIPS Instruction Set Architecture

MIPS is a CPU instruction set architecture (ISA) with a long history of development and usage. It is is one of the first processors (CPU) architecture designs focussed on instruction set complexity reduction (RISC ISA) to achieve higher instruction procession throughput per cycle (IPC) at higher clock frequencies. The architecture has undergone many enhancements and changes from its original design which corresponds to instruction set changes. The original instruction set is as well referenced as MIPS I to distinguish it from later versions now. The first CPU design implementing this architecture is MIPS Computer Systems' R2000 processor which is why original instruction set is also referenced as MIPS R2000. A goal of this thesis is to implement a visual tool which allows learning basic CPU concept. That is which the only subset of R2000 ISA is implemented and described.

Only information and concepts relevant to the selected architecture subset are described in details in the Section 2.1 and later. Everything described in this chapter is implemented in simulator unless stated otherwise.

MIPS ISA is designed as a RISC. It contains set of instructions that are supposed to be easy to implement and fast to execute. It is common that all instructions take single CPU cycle to execute (at least if we ignore pipelining and memory access). In case of MIPS ISA all instructions also have the same fixed size (32 bits).

Architecture of MIPS is divided to core instructions and four extensions. These extensions are called coprocessors. Following coprocessors are defined with their usage[1]:

- Coprocessor 0 (CP0): Virtual memory system, exceptions handling and CPU states including switching between kernel, supervisor and user states.

- Coprocessor 1 (CP1): Floating point unit

- Coprocessor 2 (CP2): Free for platform specific usage (extensions added by chip manufacturer)

- Coprocessor 3 (CP3): Reserved for MIPS ISA extension

These coprocessors are not analyzed in this thesis because they are out of the education scope and because of that they are not implemented in simulator.

## 2.1 Data Formats

MIPS I specifies and works with three data sizes [1]:

- Byte: 8 bits

- *Halfword*: 16 bits or two bytes

- Word: 32 bits or two halfwords or four bytes

Bytes in halfword and word type can be configured in either big-endian or littleendian order[1]. In case of big-endian first byte is the most significant one. For littleendian is first byte the least significant one. Simulator developed as part of this thesis implements big-endian operation and instruction set variant. That is default mode in which is CPU initialized and because of not implemented coprocessor 0 there is no possibility to switch it to little-endian.

In some operations in CPU, such as comparing of values, there is a requirement to recognize if data is signed or not. This is explicitly given by instruction specifying given operation. It is also important to note that two's complement signed number representation is used[2].

Some operations such as data load from memory or data store to memory require size type change. Change is either to make type data type smaller, which is done by dropping more significant bytes, or to make bigger data type. In such case there are two approaches. One is for unsigned values. Those are extended by zero bytes. The other one is for signed values. Sign extension is required. That is operation after which initially negative value stays negative even if additional bytes are prepended[3].

MIPS ISA also specifies data types for floating point numbers but those are not relevant to this thesis as FPU is not implemented.

## 2.2 Registers

MIPS instruction format addresses thirty-two 32-bit general purpose registers where some of them has special use.

Register 0 is hard wired to value zero. Result of any instruction writing to it is discarded and any read is read as zero value.

Register 31 is used as destination register by jump/branch and link instructions (see Section 2.3.4). Its usage in these instructions is explicit and not specified in instruction it self. These instructions are not implemented yet. Therefore this register is in reality like rest of the 29 registers.

On top of the 32 general purpose registers there are other special purpose registers. All with 32-bit size.

The primary one is program counter register. This register is used to store address to executing instruction. It cannot be directly modified (at least not without using coprocessor) but it is instead incremented automatically and modified through jump and branch instructions.

There are two other registers used during multiplication and division. Those are HI and LO. Where HI is called as higher result and LO as lower result. These registers are used in following described situations:

- Both HI and LO are used to store product of integer multiply in case of multiplication.

HI contains higher word and LO contains lower word.

- LO stores quotient and HI stores remainder of integer divide, in case of division.

Separate instructions to move to values from and to HI and LO registers are provided by MIPS ISA. Exact instructions using LO and HI are not discussed later in this text as they are not strictly required for the purpose of this thesis.

#### 2.3 Instruction Formats and Instructions Description

MIPS ISA specifies three instruction formats. They are identified as R, I and J. Their binary format is as can be seen visualized in table 2.1.

| Type | Format     |          |          | (bits)    |          |              |

|------|------------|----------|----------|-----------|----------|--------------|

| R    | opcode (6) | rs $(5)$ | rt (5)   | rd (5)    | sa $(5)$ | function (6) |

| Ι    | opcode (6) | rs $(5)$ | rt $(5)$ | immediate |          | (16)         |

| J    | opcode (6) |          | addre    | ess       | )        |              |

**Table 2.1.** MIPS instructions binary formats.

An *opcode* field in instruction are top most 6 bits containing operation code. This operation code is for initial identification of instruction. Some of the R instructions share the same operation code and in such case *function* bits are used to fully decode type of instruction.

rs, rt and rd are 5 bit wide identifiers of used general purpose register. rs is a shortcut for source register, rt is a shortcut for target register and rd is a shortcut for destination register. rs is always, as the name suggests, a data source. It means that it is always read. rd is always written to but only R instructions have this field. In case of I instruction type rt is used instead instead as destination register except for memory store operations where it specifies the second source register. In case of R instructions rt is read.

sa is used for shift instructions. This 5 bits wide field contains number of bits to be shifted.

*function* is 6 bits wide identifier that together with *opcode* defines instruction type.

*immediate* is 16 bits wide field containing constant to be used in operation specified by given instruction.

*address* is 26 bits wide field with low address bits for jump instruction. J format is used only for jump instruction and provides a way for long jumps without need of jumping by register value.

In following subsections some of the MIPS instructions<sup>[4]</sup> are described. They are grouped together by type.

#### **2.3.1** Arithmetic Instructions

Arithmetic instructions implement arithmetic operations applied on values from rs and rt registers and writing result to rd register, at least in case of R instruction type. Some of them are I instruction type and therefore use *immediate* value instead of rt as source. Not all arithmetic instructions are implemented in simulator because they are not essential for education. Because of that only few selected ones are noted and described here.

Instruction ADD and its variants ADDU, ADDI and ADDUI serve for adding two numbers. Given instruction does unsigned addition in case of appended U after base ADD. Arithmetic exception is raised when a result of the addition of two signed operands overflows 32-bit second complement representation range. Doing the same with unsigned addition doesn't cause exception and instead it results to overflow (33-th bit is dropped). Instruction is using format I instead of R when I is appended. Second operant used for adding is not from general purpose register but it an immediate value stored in the instruction itself in such case.

Instruction SUB and its kin SUBU serve for subtracting numbers. Appended U serves same purpose as in case of ADD that means it is saying that it is unsigned subtraction. And unsigned subtraction cannot cause exception unlike signed one.

Last instructions to be noted here are SLT and its variants SLTU, SLTI, SLTIU. Those compare value from register rs with value from register rt and boolean result (either

value 1 or 0) is stored to rd. In case of appended I to SLT it is same as for ADD. Meaning that second operand is replaced by value from instruction it self and rt is used as output instead. In case of appended U instruction does unsigned comparison. Difference between unsigned and signed comparison is in what ever values with most significant bit set are considered as bigger than the ones with cleared one or not. In other words if value should be considered to be unsigned or not.

#### 2.3.2 Logical Instructions

Logical instruction implement boolean operations [5]. Except for different type of operation they are same as arithmetic instructions. They are also mostly of R instruction type. And they too use rs and rt registers as source of values operation is applied on. And result is too written to rd register. Exception for I instruction types applies here as well, where the immediate field from instruction itself is used as second operant.

All logical instructions apply some boolean operation on bit by bit basis. N-th bit from source values are combined according to operation and result is placed again to N-th bit. That is done for all 32 bits. In case of AND instruction conjunction is used. For OR instruction disjunction is used. There are also NOR and XOR instructions. Those implement negated disjunction and exclusive disjunction respectively.

There are also immediate versions of some of these instructions. As noted already those are of I type and the one of the inputs is used as value from immediate field of instruction instead of rt register. In contrast to arithmetic instructions *immediate* field value is zero extended instead of sign extended. These immediate instruction variants are ANDI as analogue for AND, ORI as analogue for OR and XORI as analogue for XOR.

#### 2.3.3 Shift Instructions

Shift instructions serve for logical and arithmetic shifts[6].

Half of shift instructions take value from general purpose register rt, apply shift by sa value and writes result to rd general purpose register. Instructions SLL and SRL do left or right logical shift respectively. Instruction SRA does arithmetic right shift.

Instructions SLL, SRL and SRA has also variants SLLV, SRLV and SRAV for shifts by value from general purpose register rs. They don't use sa value from instruction.

#### 2.3.4 Branch and Jump Instructions

Branch and jump instructions manipulate program counter. Jump instructions do it unconditionally while branch instructions compare selected register values.

There are two primary jump instructions: J and JR. J instruction is of J instruction type and does absolute jump in current memory section. This section is specified by upper four most-significant bits in current program counter value. JR is a R instruction type and also is an absolute jump but compared to J it can jump anywhere in memory (using complete 32 bit addressable space). Target address is given by value in general purpose register *rs*.

There are following branch instructions: BEQ, BNE, BLTZ, BGTZ, BLEZ and BGEZ. They all are of I instruction type. BEQ and BNE instructions compare two registers (rs and rt) and if they are equal or not respectively then sign extended *immediate* value is added to current value of program counter. Instructions BLTZ, BGTZ, BLEZ, BGEZ compare only single general purpose register (rs) against zero. Otherwise if condition is met then same as in case of previous branch instructions sign extended value of *immediate* is added to program counter value. For BLTZ is condition if value is less then zero. In case of BGTZ is condition what ever is value greater then zero. For BLEZ and BGEZ conditions are if value is less or greater respectively or equal to zero.

MIPS ISA also specifies jump/branch and link instructions. Those use general purpose register 31 for storing original address before changing program counter.

#### 2.3.5 Load and Store Instructions

Load and store instructions are two types of instructions for receiving and storing data from and to memory. Those are instructions of I type. Register rs is used as a source of address. And register rt is used either as source for value to be written in case of store instruction or value loaded from memory is written to it in case of load instruction. Immediate field in instruction is used as an offset to address, it is added to value from rs register.

To receive data from memory a load instruction like LB, LH or LW exist. Second letter in these instruction names correlates with data type to be loaded. Meaning LB loads byte, LH loads half word and LW loads whole word. When type that is less than word is loaded then it is sign extended to whole word (more about that can be found in Section 2.1). There are also derivate instructions LBU and LHU where U stands for unsigned. Those zero extend value instead of sign extend. Instead missing bites are filled with zeroes.

To store data to memory a store instructions like SB, SH and SW exist. Second letter in these instruction names correlates with data type same as in case of load instruction. But there are no unsigned variants of store instructions as they are not required. When word is stored as byte then only least-significant byte is stored.

#### 2.3.6 Move Instructions

Move operations implement various transfer operations between various registers. There are two types of such instruction that are implemented in the simulator. These are instructions moving value from/to LO and HI registers to/from general purpose ones. Second type are conditional moves.

Instructions MFHI and MFLO are moving value from HI and LO register respectively to general purpose specified in *rd*. Instructions MTHI and MTLO do opposite move. They move value from general purpose register specified in *rs* to HI or LO register respectively.

Then there are MOVZ and MOVN instructions. Those conditionally move value from general purpose register rs to general purpose register rd. Condition is either if value in register rt is zero for MOVZ or non-zero for MOVN. If condition is not met then move is not realized.

Part of this category is potentially also instruction LUI. In MIPS manual it is placed together with logic instructions but that is mostly because of its possible implementation. Its usage is for setting constants to register's more-significant half word. 16 bits of instruction immediate field are shifted left by 16 and lower 16 bits from value from rt register are concatenated. Result is stored in general purpose register rt.

#### 2.3.7 Pseudo Instructions

Not all instructions have to be implemented explicitly in hardware. Some of them are defined in MIPS assembler. Compiler recognizes them but they are just special cases of other instructions. Or they stand for combination of other instructions[7].

There is NOP instructions that have no effect on CPU state when executed. It's also called as no operation. It is R instruction type and is an idiom for SLL instruction with all fields set to zero. In the other words its binary representation is all bits set to zero.

Another pseudo instruction is MOVE. This one is for copying value from one general purpose register to another. It is implemented using ADD instruction by adding register zero with source register.

Also there is a BLT pseudo instruction called branch if less then. It completes set of compare and jump instructions. It is implemented using SLT and BNE instructions.

One additional branch pseudo instruction is B. It's unconditional branch and it is implemented using BEQ instruction by comparing register zero (it is same register and because of that values are always equal).

The last pseudo instruction is LA called load address. It is intended for loading constant address (whole word) to general purpose register. This has to be done by two instructions and in common it is implemented with combination of LUI and ORI instructions.

### 2.4 Pipeline Architecture

MIPS ISA was designed with goal to achieve pipelined execution. In general it is possible to divide instruction execution to almost any arbitrary number of discrete operations. In case of basic MIPS architecture implementation, division into five stages of the pipeline is used. These stages are called[8]:

- Instruction Fetch (IF)

- Instruction Decode (ID)

- Execution (EX)

- Memory (MEM)

- Write Back (WB)

In instruction fetch stage the instruction is loaded from program memory from program counter's address. This automatically increments program counter by 4 unless previous instruction was jump or successful branch.

Instruction decode stage contains instruction decoder, registers file and compare logic used for branch instructions. In this stage the instruction is used for generating signals for this and all following stages. That is instruction decoder's job. Register identifiers rs and rt are used for getting values from given registers and *immediate* instruction field is sign extended to 32 bits.

Execution stage contains ALU. It operates on top of two 32bit values and outputs another 32bit value as a result. For some operations it also updates HI and LO registers. Values passed to ALU are values loaded from registers from instruction decode stage. In case of I instruction type second value, that would be loaded from rt register, is replaced with sign or zero extended value from *immediate* instruction field from decode stage. What ALU operation is used is defined by signal passed from control unit from decode stage.

Memory stage is dedicated for memory access. As an address is used ALU output from execute stage. For write instructions, the value to be written is value from register from rt passed through execute stage from decode stage. For more in depth information on memory access please see section 2.5. Both output from memory and ALU output are passed to next stage.

Last stage is write back. In this stage is either output from ALU or from memory written to rt or rd register (depending on instruction type).

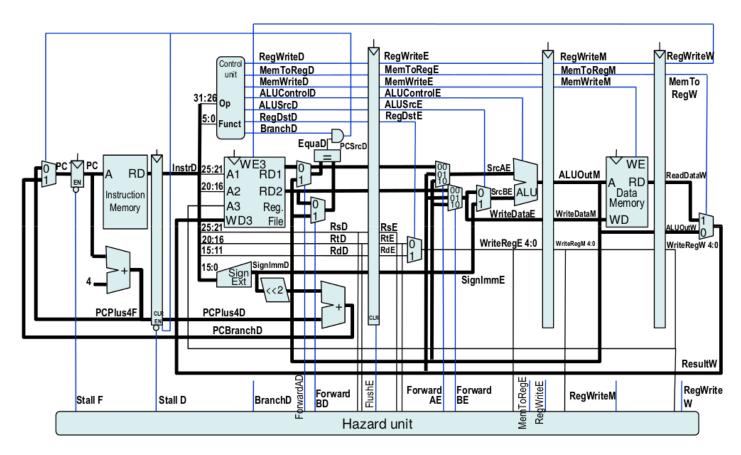

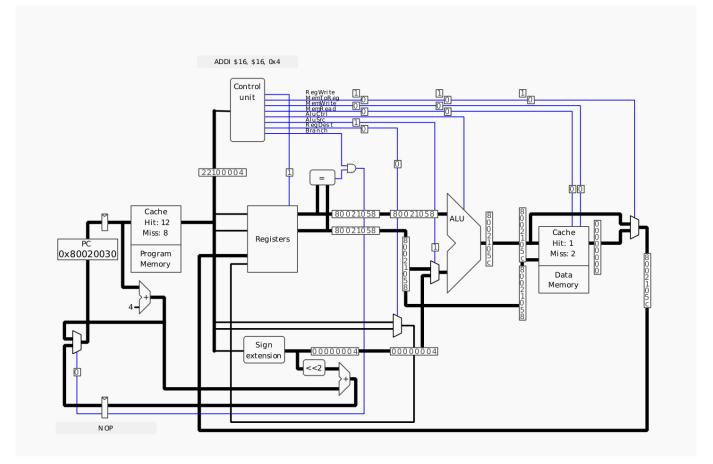

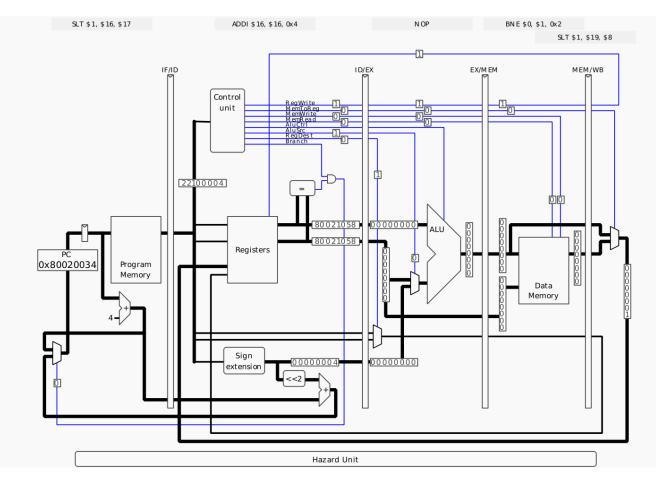

Figure 2.1. Scheme with pipelined CPU as is taught in course Computer Architectures (Source: presentation number four from this course[9]).

With instruction execution divided to stages it is possible to implement pipelined processor. This is architecture where subsequent instructions are evaluated in parallel in different sections of CPU. This means that single instruction needs five CPU cycles to complete but one instruction is always completed every cycle except for special cases. This allows faster CPU clock speed because every single stage needs less time to process instruction than all stages combined. This division of instruction processing logic enables to execute up to five times more instructions in the same interval as if the whole instruction is executed in one cycle. But such speedup would require ideally balanced pipeline design.

Pipelined architecture introduces some obstacles. Specially, for branch instructions we can't decide what instruction should be loaded next in instruction fetch stage alone. Instruction itself has to be decoded and that makes fetch stage too complicated and longer to resolve. This problem is called control hazard or branch hazard. Simple solution is to insert NOP instructions to pipeline until we decide what next program counter value should be. But this decrements pipelined speed gain. MIPS architecture instead solves this problem simply by accepting that following instruction after any jump or branch instruction will be always executed. Such instruction is in so called delay slot.

Another obstacle in pipelined architecture are data hazards. Impact of data hazards has to be analyzed and prevented for pipelined architecture. It is a problem where instruction requires an input output from some previously executed instruction. Results from two previous instructions cannot be read from registers as they are still in pipeline. Because registers are read in decode stage and previous problematic instructions can be in that case in execute and memory stage. There is also another possible instruction in write back stage. But because write back usually consist only of single multiplexer there is enough time to propagate new value to registers before they are read[8].

The possible data hazards can be accounted and resolved in program compilation phase for a simple pipeline. But such solution prevents future microarchitectural changes and leads to more wasted cycles (bubbles) when pad (NOP) instructions are inserted. It makes compilation and manual program writing much more complex as well. Another solution is to include hazard unit in a CPU design which can resolve hazards by stalling pipeline or forwarding results between instructions.

Table 2.2 contains all possible situation when hazards can occur in MIPS I with 5stages pipeline design. There are two types of instructions in sense of possible hazards. Those of which we know their result in memory stage. Those are exclusively all load instructions. And those of which we know their result in execution stage. Those are all instructions modifying general purpose registers and at the same time are not load memory instructions. For all instructions we need their inputs at the end of instruction decode stage. In table 2.2 instruction currently being decoded (being in instruction decode stage) requires content of register that is supposed to be changed by previous instruction. Columns of table are possible positions of such instruction in pipeline.

|                               | EX      | MEM     | WB        |

|-------------------------------|---------|---------|-----------|

| Result known in execute stage | Forward | Forward | No hazard |

| Result known in memory stage  | Stall   | Forward | No hazard |

Table 2.2. Hazard resolve map

### 2.5 Load/Store Architecture

MIPS ISA uses load/store architecture. Instructions to access memory are strictly separated from rest of ISA. Such memory instructions are designed to be specialized and not to have any side effect except of memory manipulation. There are two types of such instructions. There are load instructions for receiving values from memory to registers. And there are store instructions for storing values to memory.

Such architecture simplifies implementation and compiler optimization [1]. It also limits possible additional data hazards (see Section 2.4). If the data can be loaded and manipulated or even stored (read-modify-write) by single instruction (usual case of CISC designs), then pipeline has to be prolonged, or instruction folded multiple times through pipeline which makes the design much more complex. Because of load/store architecture, where value can be either read or written but not both, its possible to completely ignore memory as a source of hazards.

MIPS ISA specifies 32 bit address size and 32 bit native data type. That means that words can be interchangeably used as both data and addresses. But it also in design limits amount of memory accessible.

#### 2.5.1 Cache

Although load/store architecture forces by its design less memory intensive operations (data has to be held in general purpose registers and are moved to memory only if it is really necessary) it doesn't mitigate the core problem, that is slow memory in comparison with the rest of the CPU. For this purpose caches are used[10].

Cache is specialized data storage with fast access times that tries to serve as memory copy. It has limited size so it can't be complete copy but storing at least some of the data that were lately used improves overall memory access times. When memory is accessed through cache then there are two possible results. Either requested data were lately used and are still stored in cache or they were not recently accessed and are available only in memory it self. First case is called cache hit and second one is called cache miss. Commonly cache hits are resolved in just a single CPU tick. When cache miss is encountered it commonly takes considerably more time than cache hit.

Cache it self is constructed using value store paired with additional meta informations. At minimum cache has to have memory address identifier, called tag, of that specific value stored. On top of that it has to have bits signaling if it contains valid value and in some cases also dirty bit is required (will be addressed when write-back policies are considered). When there is read request then cache checks if it has value with validity bit set and tag matching address and if so then it provides given value instead of accessing memory it self.

Having only one value store makes unefficient cache. Because of that caches are constructed from multiple of such value stores. There are few ways those can be grouped together to create bigger cache.

One way is to just add more separate value stores. This describes parameter called *Degree of associativity* or number of ways through cache. When cache is accessed then it goes through all of its values and looks for valid one with tag matching with address. When there is no match then it looks for first one that is not valid and uses that one to get value from memory and storing it there. When all values are valid then it applies replacement policy and replaces one (changing value and corresponding tag). If there is no expansion of this cache (as described in following paragraphs) then it is called fully associative cache.

Another way is to just increase size of value storage. In that case we can store multiple words in a single store. Words stored on top of directly requested one are those that are on addresses right next to it. This divides memory to blocks of words that are loaded to cache together. It also shortens required size of stored tag because in that case we don't have to look for exact address match but just for address that exactly identifies memory block. Parameter specifying number of words to be used is called *Block size*.

The last way we can expand cache is by adding so called sets. Those are additional value stores with separate tag and other needed bits. They makes stored tag shorter same way as having higher Block size. It also archives it by almost same method. Low part of the address exactly specifies what set should be used and that way it is possible to not store those bits in tag.

When all value stores are marked as valid and tag from none of them matches the needed address (cache miss is encountered) then there is need for replacement. One of values in cache has to be replaced with value from memory from requested address. Unfortunately it is not directly defined which one should be replaced in case of higher than one degree of associativity. There are multiple algorithms to choose which one should be replaced. This thesis is concerned only with three basic ones:

Random

Least frequently used

Least recently used

Cache entry to store data is chosen randomly in case of random algorithm. It is one of the simplest possible algorithms as there is no need to store any additional information. Another two algorithms require some additional information about cache. They are based on collected access statistics. Difference is what kind of statistic is used. In case of Least frequently used it is just simple counter tracking number of accesses. In case of Least recently used it is time stamp updated every time field is accessed. For both algorithms it is desirable to replace the store with the lowers statistic. In case of Least frequently used it is the one accessed lowest number of times. In case of Least recently used the one replaced is the one with oldest access time.

It is question what should be done with value that is currently stored there in case of replacement. There are two possible approaches. One allows immediate override. Other one requires write to memory.

First approach where we can just override current value without any additional action is called Write through. Using this requires every cache value change to be also written to memory. In this case there is no need for dirty bit.

Second approach is where changed value has to be written to memory before it is overwritten. This is because all write requests just modify value in cache store but not in memory. This lowers memory load on writes but it requires additional logic that in case of cache replacement writes changed value back to memory.

# Chapter **3** Features Required for Education

Goal of this thesis is to implement application for education. Because of that it is beneficial to first look at existing tutorials as those describe minimal requirements to replace currently used software. If those are fulfilled then migrating from previously used simulator to a new one, that is implemented as part of this thesis, should be much easier. Only change might just be need of screen-shots replacement in documentation for students.

The application is intended to be used in course on Computer architecture at CTU[9]. It is an introduction course taught as part bachelor programs. Students are introduced to problems in CPU design. Course starts with basics such as arithmetics in computers and simple CPU design. It deepens this knowledge with memory access cache, pipelining and I/O. All this is demonstrated on MIPS architecture. Course also goes through other CPU architectures but for purpose of this thesis MIPS is the important one.

MIPS is used primarily because of its simple to decode and simple to understand instruction coding. It is easier to explain concepts to newcomers when instruction are coded in simple and stable way. It might be too confusing if used instruction coding would not have stable coding. Meaning if same bits in different instructions would be used regularly to code different information. But primarily it is architecture that is already used at the moment in course and intention of this thesis is not to replace it.

Relevant tutorials are described in following sections in this chapter. Not all taught tutorials are described here and some of them have wider reach than described. Some of them are also taught as not as single tutorial but multiple ones. In general following sections just contains themes and simulator usages in those tutorials that are relevant to this thesis.

#### 3.1 Tutorial Illustrating Basic CPU Structure

This tutorial is initial introduction to MIPS. It is taught in the third week. In initial weeks students are only introduced to some motivational examples and to computer arithmetics.

Students are primarily introduced to MIPS assembly language as for most of them it is first contact with assembly what so ever. Students are presented with following instructions:

- ADD

- ADDI

- SUB

- $\blacksquare$  BNE

- $\blacksquare BEQ$

- $\blacksquare$  SLT

- SLL

- **J**

- LW

- **SW**

- LUI

- JR

JAL

- JAL

Please refer to chapter about MIPS architecture (2) for description of these instructions. These instructions are minimal set that simulator has to support (except of course LA as that is pseudo instruction).

Students are provided with tutorial and presentation how to write simple assembly language program and how to rewrite basic C program constructs to MIPS assembly. Those are if-else statements and while and for loops. They are primarily presented to introduce assembly language to students. They are expected to already know uses of these constructs in C.

For these types of examples it is required that students can see compiled code in simulator while it is executed. Primary feedback for these code snippets is also from program counter and secondary general purpose registers. Students are expected to understand link between program counter and executed instruction. And they should be able to track and predict program flow in memory.

Also not to confuse students it is preferable not to use pipelined CPU and caching. Explaining delay slot on top of assembler is enough.

Next task is to analyze and write code operating on data memory using the load and store instructions together with load address pseudo instruction. Example like incrementing values in array is used to illustrate their usage.

To correctly visualize example of memory access it is required to present content of memory in simulator. This is not same as visualizing program loaded to memory but it can be implemented almost the same way because both program and data are in same memory. Only needed difference is to instead of doing reverse instruction decoding (decoding instruction to their assembler representation) to just display values in hexadecimal format.

For user friendliness of simulator it would be beneficial to also allow other numerical formats. For example showing values stored in memory in decimal or binary format. Because one of the goals of previous tutorial was to teach students conversions between numerical systems it is not beneficial for usage in this course. Not having easy automatic numerical conversion is a way to force students to do conversions outside of original lecture.

#### **3.2** Memory Access and cache Usage Tutorial

This tutorial interactively presents cache usage for memory access. Students are presented with problem of slow memory access and cache is presented as a solution. It is interworking is explained and parameters defining size and behaviour of cache are presented (they are described in Section 2.5.1). For purpose of standardized parameters description following format is established: "Size/Block size/Degree of associativity". This format is also used in following paragraphs. It fully describes size and topology of cache, at least in limits of required simulator abilities.

Students should have prepared code from previous lecture. In that lecture they are presented with Bubble sort algorithm[11] and are instructed to rewrite it to MIPS as-

sembler. This algorithm is then used in this lecture to test various cache configurations. As a reference cache implementations are used following configurations:

- 4/1/1: This one is called directly mapped cache

- 4/1/4: This one is called fully associative

- 4/1/2: This one is called cache with limited level of associativity

Students are also instructed to test other combinations of parameters and to find out optimal cache for their algorithm.

Simulator is required to have some cache content visualization and whole cache simulation has to be configurable enough to allow wide range of settings as used in this tutorial.

#### **3.3** Pipelines and Hazards Tutorial

This tutorial introduces pipelining and problems caused by it (those were in depth described in Section 2.4. Students learn about five execution stages and their possible parallel execution. Then they are presented with data hazards. Hazard unit is introduced and described.

Later in tutorial students are provided with MIPS assembler code that they should edit so it can run on CPU with pipeline but without hazard unit. That should give students understanding what kind of problems hazard unit exactly solves and how overcoming them by hand in program can be inefficient.

To ensure that compiler won't interfere with students code they are supposed to include directive .set noreorder in their code. That ensures that compiler won't be adding or moving any instructions to fill in delay slot.

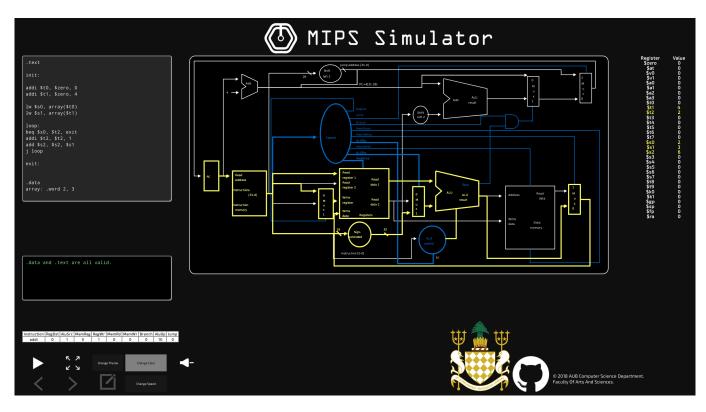

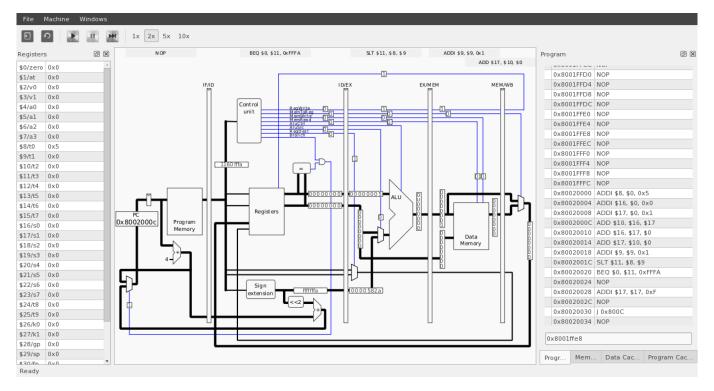

To support this usage with simulator it is required to have pipeline scheme and of course also support for pipelined CPU.

Original simulator had scheme visualisation only for pipelined CPU. Because students are using implementation without pipelining in previous tutorials, a scheme visualisation for non-pipelined version has been implemented. Having them all use CPU scheme without pipelining and them presenting them with scheme with it should give them deeper understanding of presented difference.

## 3.4 Memory Mapped I/O Tutorial

This is last tutorial in which is MIPS simulator used. It's the one presenting memory mapped I/O. Students are presented with concept of memory mapping and with inputs and outputs from CPU. Meaning interacting with external electronics. To illustrate this currently used simulator provided eight lights and eight switches. They are mapped to single byte on address 0xBF900000. Students should blink with these lights provided pattern. And as next step they should be able to read switches state and use it to select pattern to light up.

To implement this, simulator should have dedicated view for lights and switches. Those should reflect writes and reads to some specific memory address. Having that specific address configurable same as what kind of I/O is used would be beneficial.

Requirements for this tutorial are not fulfilled as part of this thesis. It is outside of this thesis assignment. It is noted here for completeness and as a reminder that this is missing for complete replacement of previous simulator.

# Chapter **4** Existing MIPS simulators

There are multiple already existing simulators. This chapter lists existing relevant applications and why their usage is not satisfactory for both education and as code base for this thesis.

Except of already used simulator, MipsIt, all other simulators missed some required feature. Most of them are open-source. Next section discusses which features each of them lacks and why none of them has been used as a base for this work. In general for most of these simulators it falls to same reasoning. To add missing features such as for example schematic view of CPU ELF file loading or cache it would require to heavily modify existing code to allow needed features. It means complete redesign of base code of application in all cases. This would mean that it would be necessary not only to come up with new base code but also on top of that to study existing. That would almost doubled the work and gain in case of using an existing code base would be mitigated.

## 4.1 Mipslt

This is currently used simulator. It contains three simulators together with integrated development environment (IDE) [12]. Those three simulators differ in what CPU they simulate. The simplest one simulates single-cycle CPU and it is simply called *Mips*. Then there are two simulators implementing CPU with pipelining. One of them doesn't implement hazard unit and is called *MipsPipeS* and other one does and is called *MipsPipeXL*.

MipsIt was developed for Microsoft Windows around year 2000. This makes it fairly old program and it has problems to run on new versions of Windows. Primarily it has to be run with Wine<sup>1</sup> on Unix systems. Together with not running on native platform and probably some left over bugs and no following development it now starts to be more and more problematic. It often crashes and it has problems with simulations restarts. Fixing these problems is not easy or even possible as MipsIt is closed source.

It serves as the baseline for this thesis because this program is currently in use and this thesis plans to replace it. Not all features are required so this thesis doesn't copy it but it is heavily inspired by it.

<sup>&</sup>lt;sup>1</sup> https://www.winehq.org/

4. Existing MIPS simulators

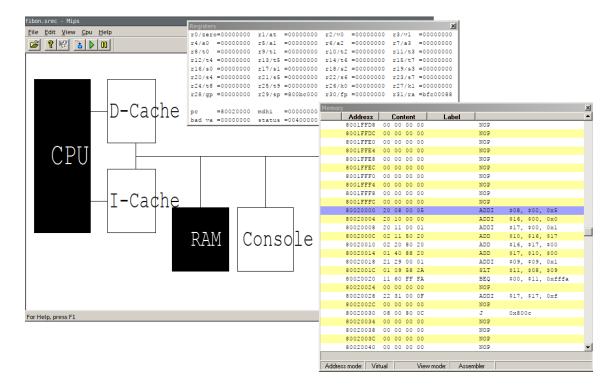

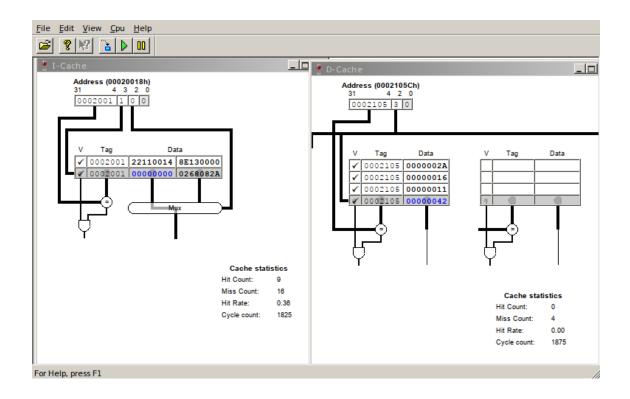

Figure 4.1. MipsIt simulator's graphical presentation of registers and memory.

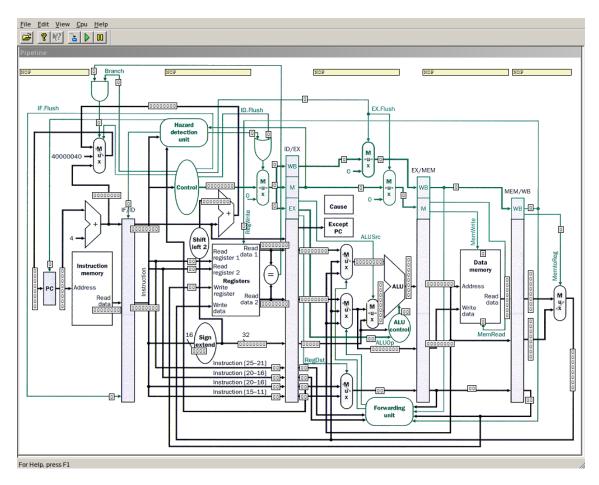

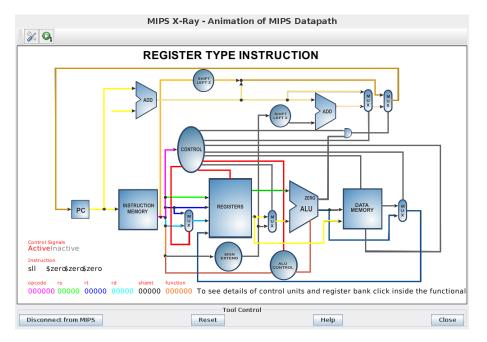

Figure 4.2. MipsIt presentation of pipeline in MipsPipeXL.

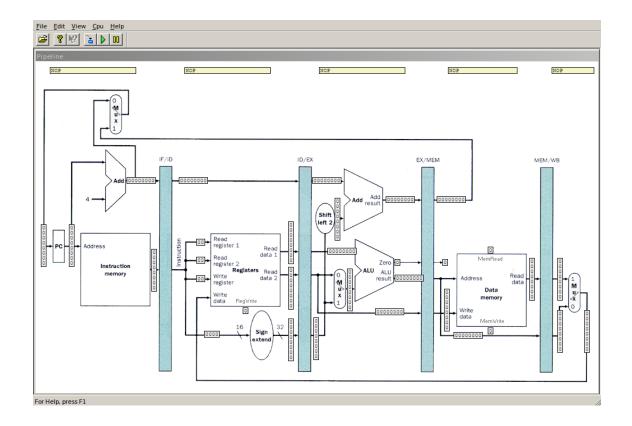

Figure 4.3. MipsIt presentation of pipeline in MipsPipeS without hazard unit.

MipsIt is only simulator described in this thesis that has cache simulation. It simulates isolated instruction (program) and data cache. Parameters such as their size, associativity or policies can be configured. MipsIt also tracks cache usage statistics. Hit and miss count with hit rate is displayed and updated in simulator.

MipsIt simulators expect input in SREC file format[13]. It can be obtained using MIPS compiler and program objcopy. This means that GCC can be used to compile code for MIPS and then it can be run in MipsIt.

Figure 4.4. MipsIt cache visualization. Instruction cache is on the left and data cache is on the right.

## 4.2 QtSpim

$QtSpim^1$  is probably the closest candidate on using it as a code base for this thesis. It's implemented in C++ and base on Qt library. It's licensed under copy-left BSD license <sup>2</sup>. It has complete MIPS CPU implementation including some very advanced features for a simulator such as operation system support. It shows memory in nice and compact way.

Between required but missing features belong cache simulation and CPU circuitry view. It also only loads assembler code. This can be bypassed by simple tool that would export assembler code from ELF file but previous missing features are more problematic.

<sup>&</sup>lt;sup>1</sup> http://spimsimulator.sourceforge.net/

<sup>&</sup>lt;sup>2</sup> https://opensource.org/licenses/BSD-3-Clause

| t Regs [16] Ø 🕱                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Text 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| rc       =       0       *         ripc       =       0       *         ripc       =       0       *         ripc       =       0       *         status       =       0       *         status       =       0       *         status       =       0       *         ritatus       =       0       *         status       =       0       * | User Text Segment [0040000][00440000]           [00400004] 2745004         addiu \$5, \$29, 4         ; 183: lw %a0 0(\$2p) # argc           [00400004] 2745004         addiu \$6, \$5, 4         ; 185: addiu \$al \$p4 # argv           [00400005] 2446004         addiu \$6, \$5, 4         ; 185: addiu \$a2 \$al 4 # envp           [00400016] 0002302         addu \$6, \$6, \$2         ; 187: addu \$a2 \$al 2 \$v0           [00400016] 0002000         jal 0x0000000 [main]         ; 188: jal main           [00400016] 30000000         op ; 199: li \$v0 10           [00400020] 30000000         ori \$2, \$0, 10         ; 191: li \$v0 10           [00400018] 30000000         ori \$2, \$0, \$1         ; 90: move \$k1 \$at # Save \$at           [8000180] 001d821         addu \$27, \$0, \$1         ; 90: move \$k1 \$at # Save \$at           [8000180] 30010001         is \$1, \$2.8672         ; 92: sw \$v0 s1 # Not re-entrant and we can't trus \$spc           \$sp         [8000186] 3c21000         mfc0 \$26, \$13         ; 95: mfc0 \$k0 \$13 # Cause register           [8000190] ac240204         sw \$4, 516(\$1)         ;         97: andi \$a0 \$a0 0x17           [8000180] 3012022         sr1 \$44, \$26, 2         ; 96: sr1 \$a0 \$k0 2 # Extract ExcCode Field           [8000191] ac240204         sw \$4, 516(\$1)         ;         102: la \$a0 0x17           [8000192] 3084001         mit |