## CZECH TECHNICAL UNIVERSITY IN PRAGUE

Faculty of Electrical Engineering

**Bachelor** thesis

Petr Čížek

# Embedded module for image processing

Department of Cybernetics Thesis supervisor: Ing. Tomáš Krajník, Ph.D. Czech Technical University in Prague Faculty of Electrical Engineering

Department of Control Engineering

# **BACHELOR PROJECT ASSIGNMENT**

## Student: Petr Čížek

Study programme: Cybernetics and Robotics Specialisation: Systems and Control

Title of Bachelor Project: Embedded module for image processing

#### Guidelines:

1. Learn about an embedded module for image processing used in the department of cybernetics.

2. Learn about 'teach and repeat' methods for mobile robot navigation.

3. Modify the FPGA module, that it can implement selected method.

#### Bibliography/Sources:

[1] Krajník, T. - Faigl, J. - Vonásek, V. - Košnar, K. - Kulich, M. - et al.: Simple, Yet Stable Bearing-Only Navigation. Journal of Field Robotics. 2010, vol. 27, no. 5, p. 511-533. ISSN 1556-4959.

[2] Šváb, J. - Krajník, T. - Faigl, J. - Přeučil, L.: FPGA-based Speeded Up Robust Features. In 2009 IEEE International Conference on Technologies for Practical Robot Applications. Boston: IEEE, 2009, p. 35-41. ISBN 978-1-4244-4992-7.

[3] Pedre, S. - Krajník, T. - Todorovich, E. - Borensztejn, P.: A Co-Design Methodology for Processor-Centric Embedded Systems with Hardware Acceleration Using FPGA. In Proceedings of the 3th Southern Programmable Logic Conference. Piscataway: IEEE, 2012, p. 7-14. ISBN 978-1-4673-0185-5.

Bachelor Project Supervisor: Ing. Tomáš Krajník, Ph.D.

Valid until the winter semester 2013/2014

4 del

prof. Ing. Michael Šebek, DrSc. Head of Department

prof. Ing. Pavel Ripka, CSc. Dean

Prague, December 18, 2012

# Prohlášení

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

V Praze dne. 23.5.2013

Pfr Vich

## Abstrakt

Tato práce předkládá návrh systému pro zpracování obrazu a následnou navigaci mobilního robotu specificky navržený pro architekturu programovatelných hradlových polí (FPGA). Základem práce je popis návrhu řešení, které vychází ze specifických vlastností FPGA architektury a je jim přizpůsobeno. Část zpracovávající obrazová data je rozdělena na dvě části: detektor významných bodů v obraze vycházející z algoritmu Speeded Up Robust Features (SURF) a deskriptor významných bodů založený na algoritmu Binary Robust Independent Elementary Features (BRIEF). Obě části jsou kompletně implementovány v logice hradlového pole. Navigační algoritmus je určen pro zpracování vestavným procesorem a vychází z algoritmu SURFnav vyvinutého na Fakultě elektrotechnické ČVUT. Začátek práce je věnován teoretickému úvodu do problematiky navigace mobilních robotů a strojového vidění. V závěru práce je vyhodnocen výkon detekční části algoritmu.

### Abstract

This thesis propose a system design for image processing and mobile robot navigation specifically suitable for the architecture of the Fieldprogrammable Gate Arrays (FPGAs). The image processing part of the design consists of the image feature detector based on the Speeded Up Robust Features (SURF) algorithm and the image feature descriptor based on the Binary Robust Independent Elementary Features (BRIEF) algorithm. The image processing part is completely implemented in the FPGA fabric. The navigation algorithm is designed as a software for the embedded processor of the module. It is based on the SURFnav navigation algorithm developed on the Faculty of Electrical Engineering of the CTU. This thesis also provides the reader with the background of the mobile robot navigation and image feature extraction methods. The image feature detector part of the design is evaluated in the end of this thesis.

# Acknowledgment

I would like to express my thanks to my supervisor Tomáš Krajník. He taught me a lot and provided me with conditions and support for development of such a challenging bachelor project. I would like to thank my family for a full support throughout my studies at the Czech Technical University.

# Contents

| 1 | Intr | roduction                                                                                                                                                         | Ĺ |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2 | Visi | ion based navigation                                                                                                                                              | 3 |

|   | 2.1  | Localization                                                                                                                                                      | 3 |

|   |      | 2.1.1 Incremental localization                                                                                                                                    | 3 |

|   |      | 2.1.2 Absolute localization                                                                                                                                       | 4 |

|   | 2.2  | Mapping                                                                                                                                                           | 4 |

|   |      | 2.2.1 Map based navigation $\ldots \ldots \ldots$ | 3 |

|   |      | 2.2.2 Map-building based navigation                                                                                                                               | 7 |

|   |      | 2.2.3 Map-less navigation                                                                                                                                         | 3 |

|   | 2.3  | Motion planning                                                                                                                                                   | 3 |

| 3 | Ima  | age feature extraction algorithms 10                                                                                                                              | ) |

|   | 3.1  | Interest points detection                                                                                                                                         | ) |

|   |      | 3.1.1 Speeded Up Robust Features                                                                                                                                  | 1 |

|   | 3.2  | Interest point description                                                                                                                                        | 3 |

|   |      | 3.2.1 BRIEF descriptor $\ldots \ldots \ldots$     | 3 |

|   | 3.3  | FPGA based image feature extractors                                                                                                                               | 1 |

| 4 | Met  | thod design 16                                                                                                                                                    | 3 |

|   | 4.1  | Field-programmable gate array (FPGA) 16                                                                                                                           | 3 |

|   | 4.2  | Image feature detector                                                                                                                                            | 3 |

|   |      | 4.2.1 Integral image generation                                                                                                                                   | 9 |

|   |      | 4.2.2 Hessian detector $\ldots \ldots \ldots$     | 9 |

|   |      | 4.2.3 Scale space construction                                                                                                                                    | ) |

|   |      | 4.2.4 Interest point localization                                                                                                                                 | 1 |

|   | 4.3  | Image feature descriptor                                                                                                                                          | 2 |

|   |      | 4.3.1 Descriptor generation                                                                                                                                       | 2 |

|   |      | 4.3.2 Orientation assignment                                                                                                                                      | 2 |

|   | 4.4  | Navigation algorithm                                                                                                                                              | 3 |

|   |      | 4.4.1 Teach phase $\ldots \ldots 23$                                                        | 3 |

|   |      | 4.4.2 Repeat phase $\ldots \ldots 23$                                                              | 3 |

|   |      |                                                                                                                                                                   |   |

| <b>5</b> | Implementation 2 |         |                                                                                  | 26 |

|----------|------------------|---------|----------------------------------------------------------------------------------|----|

|          | 5.1              | Referen | nce boards                                                                       | 27 |

|          | 5.2              | FPGA    | $configuration  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 27 |

|          |                  | 5.2.1   | Pixel I/O                                                                        | 29 |

|          |                  | 5.2.2   | Feature detector                                                                 | 30 |

|          |                  | 5.2.3   | Feature descriptor                                                               | 35 |

|          |                  | 5.2.4   | Embedded processor and its peripherals                                           | 39 |

|          |                  | 5.2.5   | Implementation costs                                                             | 40 |

|          | 5.3              | Softwa  | re description                                                                   | 40 |

| 6        | -                | erimer  | <b>nts</b><br>ty test                                                            | 42 |

|          | 6.1              |         |                                                                                  | 42 |

|          | 6.2              | Perform | mance in the long term navigation scenario test                                  | 43 |

| 7        | Con              | clusior | 1                                                                                | 45 |

# List of Figures

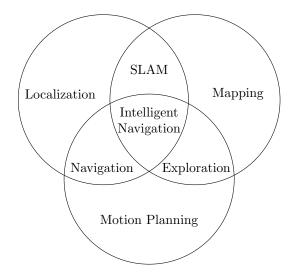

| 1  | Navigation tasks relations. Courtesy of [1]                                       | 3  |

|----|-----------------------------------------------------------------------------------|----|

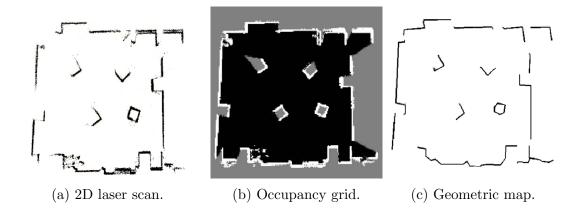

| 2  | Map examples 1. Courtesy of [2]                                                   | 5  |

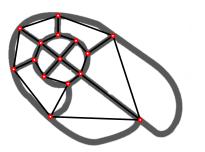

| 3  | Map examples 2                                                                    | 6  |

| 4  | Path planning using RRT algorithm. Courtesy of [3]                                | 9  |

| 5  | Integral image usage illustration. Courtesy of [4].                               | 11 |

| 6  | Discretized Gaussian kernels and their approximations. Courtesy of [4]. $\ .$     | 12 |

| 7  | BRIEF descriptor binary tests examples. Courtesy of [5]                           | 14 |

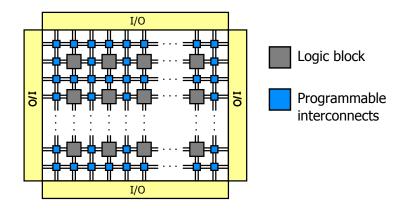

| 8  | FPGA architecture                                                                 | 17 |

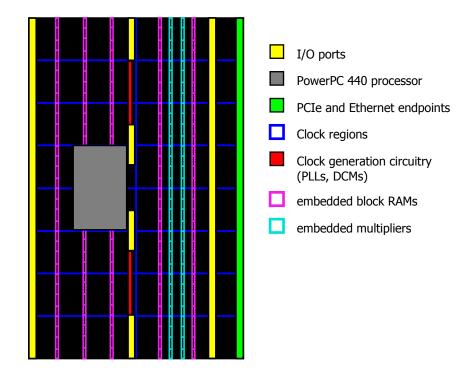

| 9  | FPGA structure.                                                                   | 18 |

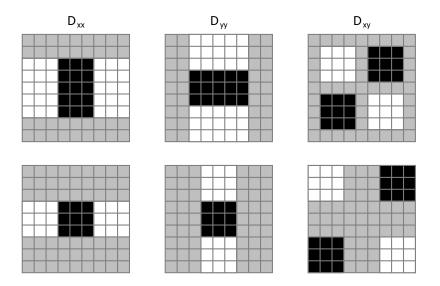

| 10 | Comparison of convolution kernels                                                 | 21 |

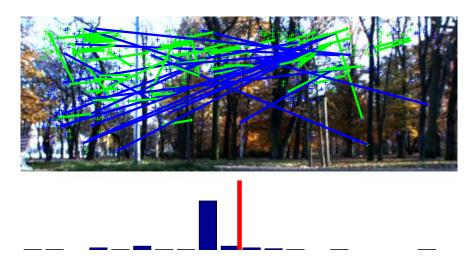

| 11 | Detected landmarks in the picture and the corresponding navigation his-<br>togram | 24 |

| 12 | Development platforms.                                                            | 26 |

| 13 | Digital video timing diagram.                                                     | 28 |

| 14 | Block diagram of the high-level FPGA architecture                                 | 29 |

| 15 | Feature detection chain architecture.                                             | 30 |

| 16 | Simplified block diagram of the PIXEL_BUFFER core                                 | 32 |

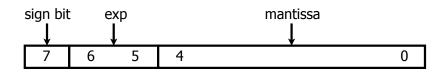

| 17 | PRELOC_MAX_FINDER result value composition.                                       | 33 |

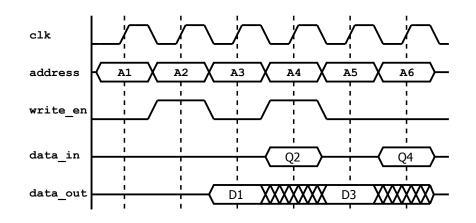

| 18 | Zero Bus Turnaround SRAM memory timing diagram                                    | 36 |

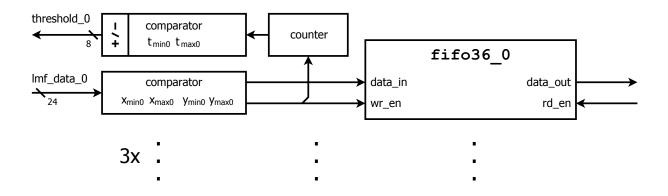

| 19 | Simplified block diagram of the FEATURE_BUFFER core                               | 37 |

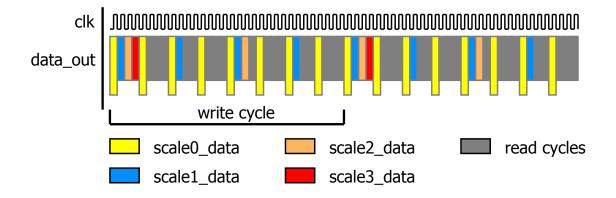

| 20 | Timing diagram of SRAM memory bus utilization during display area. $\ .$ .        | 38 |

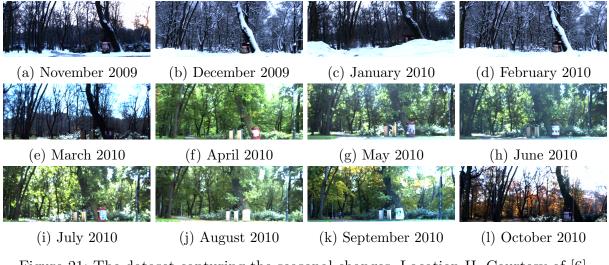

| 21 | The dataset capturing the seasonal changes. Location II. Courtesy of $[6]$ .      | 43 |

| 22 | The dataset locations. Courtesy of $[6]$                                          | 44 |

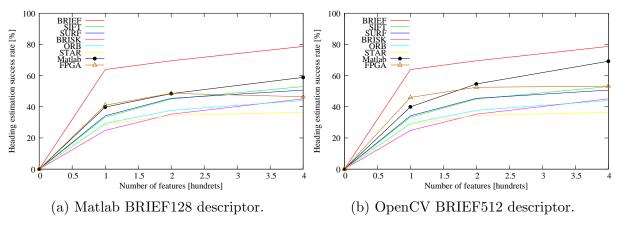

| 23 | Heading estimation success rate                                                   | 44 |

# List of Tables

| 1 | Description performance comparison           | 23 |

|---|----------------------------------------------|----|

| 2 | Segment landmark map composition             | 24 |

| 3 | Reference boards features                    | 27 |

| 4 | MASTER_CNTRL core user accessible registers. | 39 |

| 5 | Stability success rates.                     | 43 |

| 6 | CD content                                   | 50 |

## 1 Introduction

For any autonomous vehicle the ability to navigate in its environment is essential. If we take evolution and nature as examples of perfect mastery of navigation we will realize that many of the living organisms navigate themselves by sight. This is also the main motivation for building systems that can navigate themselves by means of machine vision. With the growing computational performance of nowadays computers we have seen in recent years successes like first vehicles capable of autonomous navigation in an urban area [7] or a squad of flying quad-copters capable of synchronized movement in a confined space [8]. All these systems use powerful on-board or off-board computers for navigation. However sometimes the application imposes strict restrictions on hardware dimensions or power consumption of navigation system. For example the unmanned aerial vehicles (UAVs) are a typical platform which is restricted by its lifting capacity and a power consumption. These two demands make any use of conventional powerful computer platforms or hardware acceleration on graphics cards (GPUs) unusable because they are either too big to be carried by the small mobile robot or consume too much power which make them unsuitable for the long term operation on batteries. However if we take a closer look on the vision based navigation methods the major computationally demanding part usually consist in tasks related with the image processing. In the field of mobile robotics the local image feature extraction is especially utilize. The image feature extraction algorithms are computationally intensive however processes performed by them could be easily parallelized because they usually perform same computational operations on the different sets of data. This make the image feature extraction algorithms ideal for implementation on the Field-Programmable Gate Arrays (FPGAs). The FPGA architecture allows the programmer to built custom designs specifically suitable for given tasks.

In this thesis I would like to present a novel design for the FPGA architecture which is capable of real-time visual navigation by following natural landmarks. The design consists of the image feature detector and the image feature descriptor implemented in the FPGA fabric and the navigation algorithm implemented in software of embedded processor of the FPGA chip. The motivation behind the work on this thesis is to develop small, fast and reliable architecture capable of continuous video stream processing on low-end FPGA chips.

In early stage of my work at the Intelligent and Mobile Robotics Group I originally had to follow up on the work done by Jan Šváb in his master thesis [4]. He built a custom FPGA-based camera module specifically suitable for applications in mobile robotics and implemented a complete Speeded-Up Robust Features (SURF) algorithm [9] on the device. However it has shown that his solution is very consistent and provides only minimum space for any improvements. Few enhancements were introduced to the original design in order to allow the module to be used in navigation tasks. The results of this work is in review in the article [10].

### 1 INTRODUCTION

During the work on the original design I suggested a new method of image feature detection specifically suitable for the FPGA architecture and tasks related with the mobile robot navigation. It was decided to implement and try the new design. This thesis summarizes the work done on this project which leads to the new design so far capable of real-time image processing.

This thesis is structured in four chapters. The first two chapters provide the reader with the background of the mobile robot navigation and image feature extraction methods. More attention is paid to the SURF algorithm and the SURFnav navigation method [11], [3], [1]. Chapter "Method design" describes the suggested new method of the image feature detection, the description and the navigation. Chapter "Implementation" describes the implementation of the image feature detector and the image feature descriptor in the FPGA fabric. Finally, the chapter Experiments contains evaluation of the image feature detector part of the design.

## 2 Vision based navigation

For any autonomous vehicle the ability to navigate in its environment is essential. The process of navigation could be roughly described as a process of determining suitable and safe path between the starting and the goal point. To achieve this objective the mobile robot has to solve tasks of localization, mapping and motion planning [12]. Although localization, mapping and motion planning are three different areas of interest and could be studied separately they are closely related and in the context of the intelligent navigation are often studied together. Figure 1 shows the simplified relations between these three tasks.

Figure 1: Navigation tasks relations. Courtesy of [1].

## 2.1 Localization

Localization is a process when the robot determines its position. Localization could be either incremental or absolute [13].

## 2.1.1 Incremental localization

Incremental localization, also called dead-reckoning, assumes that the starting position of mobile robot is known. During the navigation the robot estimates its current position from the previously known position and an increment of travelled distance. The biggest disadvantage of this method is that it accumulates position error over time. Most well known examples of dead-reckoning techniques are odometry or inertial navigation (i.e. navigation using accelerometers and gyroscopes). Due to accumulation errors these techniques are not suitable for long term localization, however they are usually cheap to implement and easy to use so they are fairly popular. Examples of purely vision based incremental localization methods would be visual odometry or systems based on optical flow. Visual odometry (e.g. [14]) is a process of determining robot's position using sequential camera images to estimate the distance travelled. Optical flow is a principle used by optical mouse for estimating speed and heading. On the same principle works for example the PX4FLOW Smart Camera developed by 3D Robotics which uses sum of absolute differences (SAD) method for optical flow determination between two consecutive images [15]. The advantage of visual odometry and optical flow systems is that they provide the enhanced navigation accuracy for robots using any type of locomotion on almost any surface.

### 2.1.2 Absolute localization

Absolute positioning means that the mobile robot has no information about its starting position and has to estimate its position in a global coordinate system. This method usually relies on the map of the environment in which the navigation system must construct a match between the observations and the expectations. Typically the mobile robot estimates its position relatively to the landmarks in the area. These landmarks could be either natural or artificial [13]. Natural landmarks are usually objects which are naturally present in the environment (like walls, corners, etc.). The position of artificial landmarks, which are placed manually in the environment in order to improve navigation accuracy, is usually known in advance. By vision based localization it could be various blobs or patterns whose detection in the image is more easier than the detection of natural landmarks. Another examples of artificial landmarks are active beacon systems. Beacon systems always use triangulation or trilateration for localization relatively to three or more transmitters which actively transmits signals about its position. Beacon systems consist of beacons mounted at known positions in the environment and a receiver on board of the mobile robot (or vice versa). Examples of absolute positioning beacon systems could be global positioning system (GPS) or Ubisense system [16].

## 2.2 Mapping

The problem of localization is very closely related to mapping. Systems that use vision for navigation could be roughly divided into three main groups depending on whether they use map of the environment for navigation or not [17]. These three groups are

- map based navigation,

- map-building based navigation,

- map-less navigation.

In the first two cases the mobile robot localization is based on the map of its environment. This model (map) represents knowledge about the environment. Maps could be generally divided into four main groups [1], [18]: sensory, geometric, topological and landmark maps.

Figure 2: Map examples 1. Courtesy of [2].

- Sensory maps are only appropriately represented and saved sensory data. Sensory maps are quite simple to construct but they are always memory demanding particularly when the long term navigation is performed. The best example of sensory map is a point cloud produced by laser scanner. An example of the 2D point cloud is in Figure 2a. Point cloud data could be further simplified in a form of occupancy grid. Occupancy grids represent the environment by a grid consisting of cells where each cell contains information about whether the accordant place is occupied or not. Figure 2b shows the occupancy map of a room with three obstacles the black color corresponds to traversable area, white color represents detected obstacles. In the figure it can be seen that occupancy grid maps also rely on the position of the mobile robot. Areas which are out of sight or has not been mapped yet are considered occupied (depicted by gray color).

- Geometric maps are usually built from geometrical primitives such as lines or simple bodies. These maps bring more abstraction than sensory maps and therefore occupy less memory. They are usable for example in indoor or urban environments where a lot of flat surfaces are present. Figure 2c shows the 2D geometric map of a room where obstacles and walls are approximated by line segments. An example of geometric mapping of the urban area is in the paper [19] where the authors used laser scan data of a large scale urban area and built the map from plane primitives.

- **Topological maps** are basically graphs. Nodes represent the most characteristic places of the environment and edges represent routes. Information about how to navigate from one node to the another could be bound to edges. An example of topological

(a) Topological map. Courtesy of [3].

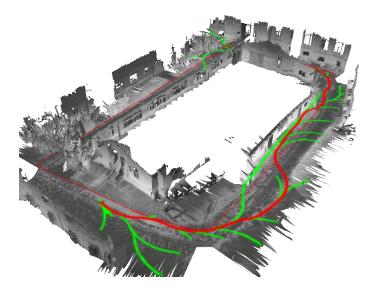

(b) Landmark map (SURFnav algorithm).

Figure 3: Map examples 2.

map would be a map of public transport system. Another example is in Figure 3a where a topological map of sidewalks in the park is depicted. An example of visual topological mapping is in the paper [20].

Landmark maps are used frequently in the field of mobile robot visual navigation. Landmark map contains information about landmarks which could be observed from given location. Landmarks should be salient points or areas in the image which are easily detectable, recognizable and traceable. Localization and navigation is done by detecting landmarks and matching them with those from the map. In Figure 3b there is a possible representation of the topological map. Black line represents the mobile robot path. Black points represent individual detected features and blue lines correspond to feature tracking during the robot's movement. The dashed red line corresponds to the current position of the mobile robot. This implies that the mobile robot should observe image features which are marked by red circles from its current position.

## 2.2.1 Map based navigation

These are systems that use map for navigation. This map is one of aforementioned types. There are two types of map based navigation systems [17]. The first one are systems that need a complete map of an environment before the navigation starts.

The second type of map-based navigation techniques are those called "teach and repeat" techniques. The map is not provided to the robot in advance but it is built by the robot during the first guided pass through the environment. In the field of visual navigation it is mainly the sensory or the landmark map.

Paul Furgale and Timothy D. Barfoot published several papers on the long term teach and repeat methods. In the article [21] they presented solely visual teach and repeat method based on the stereovision and tracking of image features. During the teaching phase the mobile robot is logging stereo images which are subsequently postprocessed into a series of overlapping submaps. During the repeat pass the mobile robot uses the database of submaps to repeat the route. The system can start at any place along the pre-learned path. The method combine topologically connected key frames (submaps) with a controller that attempts to drive the robot to the same viewpoints along the pre-trained path (visual odometry). It means that during the repeat phase the algorithm interleaves localization and visual odometry for path following. In the paper [22] they extended previously described solely visual method with laser scanners for motion estimation.

Article [23] presents a simple form of teach and repeat navigation. It utilizes a map consisting of salient image features remembered during a teaching phase and a simple leftright turn algorithm based on tracking image features for mobile robot steering during the repeat phase.

Another teach and repeat method called SURFnav [11] was developed on the Czech Technical University. The SURFnav navigation is based on the monocular vision supported by the dead-reckoning. The dead-reckoning techniques are separately not suitable for the long term localization because they accumulates position error. Therefore the mobile robot uses the vision for estimation of its position and heading. In the article [11] is mathematically proved that the heading correction itself can suppress odometric error keeping the position error bound and is sufficient for the long term robot localization. Moreover the algorithm's computational complexity doesn't grow together with the map growth which makes the SURFnav algorithm well suitable for long term navigation and embedded platforms with limited computational power.

During the teach phase the mobile robot is guided along straight line segments through the environment, measuring distance travelled by dead-reckoning and composing a landmark map of the environment. During the repeat phase the mobile robot drives the individual segments as follows. At each segment start the robot is turned to the desired direction according to compass value. During the traversal of the segment the heading of the robot is corrected based on matched visual features from the map and from the current observation. This method is called visual compass. The end of the segment is recognized according to traveled distance, which is measured by odometry.

Other examples of visual teach and repeat algorithms could be found in literature. In the paper [17] there is a brief overview of these methods.

### 2.2.2 Map-building based navigation

These are systems that build a map of the environment as they traverse through it. It means that they are self-localizing the robot in the environment simultaneously during the map construction. This is called Simultaneous Localization and Mapping (SLAM) [24]. However this procedure leads to problems that are directly connected with the nature of such algorithms. On the one hand the map building of the environment depends on accurate localization of the robot but on the other hand the robot localizes itself within that map. This leads to the observation that localization and mapping errors accumulate over time and motion. SLAM is therefore defined as a problem of building a model leading to a new map, or repetitively improving an existing map. A lot of examples of SLAM algorithms could be found in literature (e.g. comprehensive overview of visual SLAM methods is in the paper [17]).

#### 2.2.3 Map-less navigation

These are systems that do not use any map for navigation. Therefore they are also called reactive navigation systems. Navigation is only a reaction on current observation of the environment. Map-less navigation systems mostly include reactive techniques that use visual clues derived from the segmentation of an image, optical flow, or visual odometry for the navigation. Typical representative of these methods is GeNAV system [25] developed by Intelligent and Mobile Robotics Group. GeNAV is a system for unstructured roads following and crossroads recognition based on the texture segmentation of an image. The algorithm seeks the edges of the unstructured road and navigates the mobile robot in its center. If it detects the corssroad it informs the control computer.

## 2.3 Motion planning

Motion planning is a process of finding suitable and safe path between the start and the goal positions. Motion planning is usually based on results of the localization and the mapping.

By the map-based and the map-building based navigation it depends on the map. By the sensory or the geometric map the navigation can be performed for example by means of the Virtual Force Fields [26], where the goal point produces virtual attractive force and every obstacle produces virtual repulsive force, or by means of the Rapidly-exploring Random Tree (RRT) [27]. The RRT algorithm is capable of path planning for mobile robots respecting their kinodynamic constraints. In Figure 4 there is an example of path planning using RRT algorithm.

Navigation on topological maps is quite simple because it can use any graph traversal algorithm to reach the goal (e.g.  $A^*$  algorithm or the greedy algorithm)

By the Teach and Repeat methods the primary motion planning is provided by the human during the first guided pass through the environment.

Figure 4: Path planning using RRT algorithm. Courtesy of [3].

Specific kind of motion planning is exploration, when the mobile robot plans its motions in order to explore specific area. By exploration the goal is to get the mobile robot in place where it can obtain new information of the environment.

Another field of motion planning is related with formation control [28], swarm robotics [8] and agent technologies [29] where the motion planning algorithms need to plan the suitable path for more mobile robots.

There are also algorithms which do not implement any higher intelligence for motion planning. Typical example are various household cleaning robots which are not aware of the shape of the area and perform only simple random reactive navigation inspired by insect behaviour.

In conclusion the efficiency of motion planning algorithms is generally influenced by their ability to retrieve the knowledge about their environment and the ability to process these knowledge.

## 3 Image feature extraction algorithms

Image feature extraction is considered to be a high-level image processing technique, which performs operations over an image in order to extract local features, which could be either points, regions or edge segments. Local features are areas of the image, which are expected to be reliably and repeatably detectable, preferably from a wider range of camera positions. They are used in many machine vision applications such as object recognition, robotic mapping and navigation, image stitching, 3D reconstruction or video tracking.

Image feature extraction always consists of two phases: the detection and the description. The interest points detection is a process which purpose is to identify the salient points in the image. Its input are the image data and output are locations of interest points in the picture optionally together with some more information about the located point (e.g. scale, contrast, etc.) The interest point description is a process when the surrounding of the detected interest point is described in order to allow the feature matching. The feature matching is a process when the description of two points is compared in order to determine whether these two points corresponds to the same feature of the environment.

This chapter provides the reader with basic overview of commonly used feature extractor algorithms with focus on interest point detectors and related descriptors which are used in robotic navigation. More attention is paid to the Speeded Up Robust Features (SURF) algorithm, which is a part of the original implementation [4]. Separate part discusses known implementations of image feature extractors on the FPGA architecture.

## 3.1 Interest points detection

Interest points detection is a process of feature extraction, which purpose is to identify interest points in the image. A lot of algorithms have been proposed on this topic. A comprehensive overview of image feature detector algorithms is in article [30].

One of the first interest point detectors was the Moravec operator introduced in the year 1980. After that the feature detection has been a growing field in the computer vision. Moravec operator works mainly as a corner detector defining corner as a point with low self-similarity. It measures the differences between a sliding image window and windows shifted in several directions. This method is called auto correlation.

The Harris corner detector [31] is based on the Moravec operator but it is more robust to noise, intensity and rotation changes. It uses a Gaussian to weight the derivatives inside the sliding window. Several Harris-based algorithms was proposed mainly to deal with the low scale invariance of the original detector. Their overview can be found in the article [30] One of the most robust image feature detectors is the Scale Invariant Feature Transform (SIFT) detector [32] that apart from detecting features proposes a descriptor that is invariant to scale, rotation and illumination changes. It uses the difference of Gaussians for image feature detection. However fully implemented SIFT is highly computational demanding.

#### 3.1.1 Speeded Up Robust Features

The original Speeded Up Robust Features (SURF) algorithm as proposed by Bay et al [9] relies on estimation of Gaussian and Haar wavelet filter responses by box filters. It consists of four stages: integral image generation, interest point detection, orientation assignment and descriptor generation.

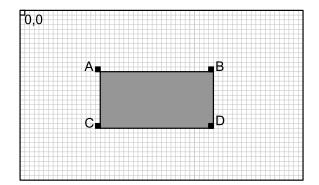

**Integral image generation** This is a key component of SURF algorithm because it significantly reduces memory and computational demands. When using integral image it is necessary to perform only four read operations in order to calculate rectangular area integral of any size. The integral image is calculated using the equation 1.

$$I_{\Sigma}(x,y) = \sum_{i=0}^{x} \sum_{j=0}^{y} I(i,j)$$

(1)

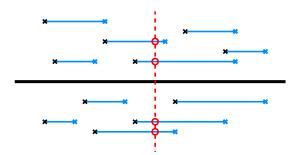

Figure 5: Integral image usage illustration. Courtesy of [4].

The usage of integral image is shown in figure 5, where the integral over the gray area is calculated using the equation 2.

$$I_{\Sigma}(ABCD) = I_{\Sigma}(A) + I_{\Sigma}(D) - I_{\Sigma}(B) - I_{\Sigma}(C)$$

(2)

Interest point detection The second stage identifies interest points by finding local maxima among determinants of Hessian matrices. Equation 3 shows definition of this determinant for a general two dimensional function f.

$$\mathcal{H}(x,y) = \begin{vmatrix} \frac{\partial^2 f}{\partial x^2} & \frac{\partial^2 f}{\partial x \partial y} \\ \frac{\partial^2 f}{\partial y \partial x} & \frac{\partial^2 f}{\partial y^2} \end{vmatrix} = \frac{\partial^2 f}{\partial x^2} \frac{\partial^2 f}{\partial y^2} - \left(\frac{\partial^2 f}{\partial x \partial y}\right)^2$$

(3)

In the case of machine vision the two dimensional function actually represents the image luminance. In the original SURF the second order partial derivatives are replaced by convolution of the image with derivatives of appropriate Gaussian kernels. Thus, the equation (3) becomes:

$$\mathcal{H}(x,y,\sigma) = \begin{vmatrix} L_{xx}(x,y,\sigma) & L_{xy}(x,y,\sigma) \\ L_{xy}(x,y,\sigma) & L_{yy}(x,y,\sigma) \end{vmatrix}$$

(4)

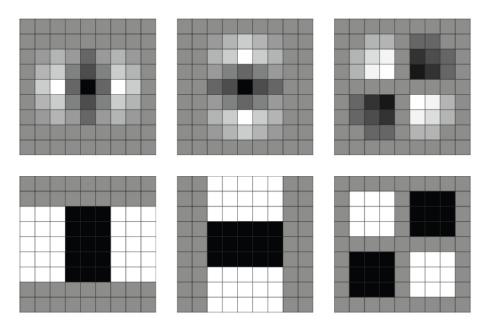

Where  $L_{xx}(x, y, \sigma)$  represents a convolution with a second order derivative of a discretized two dimensional Gaussian of variance  $\sigma$ . The SURF detector approximates the Gaussian kernel responses L with box filter responses D. Figure 6 shows the comparison of the original Gaussian kernels  $L_{xx}, L_{yy}, L_{xy}$  with their box filters approximations  $D_{xx}, D_{yy}, D_{xy}$ . Convolution of the image with these kernels is calculated much faster using the integral image. The box filter approximation allows to rewrite equation (4) as  $\mathcal{H} \sim D_{xx}D_{yy} - (0.9D_{xy})^2$ . By the SURF algorithm the coefficient of 0.9 represents the weighting mechanism which compensates the box filters approximation.

Figure 6: Discretized Gaussian kernels and their approximations. Courtesy of [4].

To achieve scale invariance the algorithm uses filters with multiple sizes. This creates a three dimensional space of determinant results called the scale space. After estimation of the Hessian determinants on all the scales for the whole image their local maxima are extracted. Located local maxima are then compared with predefined threshold. The point is declared an image feature if it passes both conditions.

- **Orientation assignment** This phase is connected with the descriptor generation. To achieve the orientation invariance, which is important in many machine vision applications, the interest point is assigned a "dominant direction". This direction is calculated from the responses of Haar wavelet filters centered around the interest point.

- **Descriptor generation** The original SURF descriptor is a 64 element wide vector of floating point numbers calculated from a square area neighbouring the interest point rotated in the direction of the dominant direction. This neighborhood is divided in 16 equal sub-squares, which are regularly sampled by Haar wavelet filters. Horizontal  $d_x$  and vertical  $d_y$  Haar wavelet responses are weighted by a 2D Gaussian function centered at the interest point. The resulting values within each sub-square are summed to form a vector  $\sum dx$ ;  $\sum dy$ ;  $\sum |dx|$ ;  $\sum |dy|$ . The vectors of all sub-squares are chained to form a vector and then normalized in order to obtain final descriptor. The SURF descriptor contains also the sign of the interest point's Hessian value in order to simplify feature matching. Since the SURF detector usually finds interest points on blob-like structures, this sign distinguishes light blobs on dark background from the opposite case.

## 3.2 Interest point description

The interest point description is a process when the surrounding of the detected interest point is described in order to allow the feature matching. The resulting descriptors can be mutually matched using their euclidean distances (or other measures). Many algorithms features their own descriptor (e.g. SIFT, SURF) however there are also descriptors which can be used with almost any feature detector. The original SURF descriptor was presented earlier in this chapter. However it takes a lot of computation operations in floating point numbers to assemble it. This is not very good for embedded applications because specialized hardware funds need to be utilized by microprocessors or microcontrollers in order to be able to process floating point numbers efficiently. Therefore some other descriptor which is easy to construct was searched for.

## 3.2.1 BRIEF descriptor

The Binary Robust Independent Elementary Features (BRIEF) descriptor was proposed in paper [5]. It is a fast to implement easy to construct image feature descriptor which uses pairwise intensity comparison of pixels inside an image patch which surrounds located feature. These comparisons form a set of unique binary tests which are subsequently stored into an  $n_d$ -dimensional bit vector. In the original paper the  $n_d$  constant takes values of 128, 256 and 512. Several different approaches to choosing the test locations are proposed in the paper. However it has shown that completely random set of binary tests performs better than any artificially created set of tests. In Figure 7 there is an example of two random sampling BRIEF and the artificially created BRIEF descriptor. The descriptor similarity can be evaluated using the Hamming distance, which is very efficient to compute.

Figure 7: BRIEF descriptor binary tests examples. Courtesy of [5].

Several improvements were proposed to the BRIEF descriptor since the original paper was published. Mainly improving the descriptor's rotation invariance. Binary Robust Invariant Scalable Keypoints [33] (BRISK) is a scale and rotation invariant version of BRIEF which uses a deterministic comparison pattern. Oriented FAST and Rotated BRIEF [34](ORB) is another attempt to achieve a scale and rotation invariant BRIEF. It uses FAST (Features from Accelerated Segment Test) as a keypoint detector. By the same authors of [5] there is an improvement of original method D-BRIEF [35] which uses discriminative projections for descriptor construction.

## 3.3 FPGA based image feature extractors

In the recent years the popularity of the FPGA based image processing has grown rapidly. A lot of articles on image processing by FPGA was published. This section lists the known image feature extractors implemented in the field programmable gate arrays.

From the FPGA SIFT implementations there are implementations by Bonato et al [36] and Feng-Cheng Huang et al [37]. Bonato et al presented a complete SIFT implementation for the Altera Stratix II FPGA capable of feature detection on images with the resolution of  $320 \times 240$  pixels in 33 ms. However they implemented the descriptor calculation in the soft-core processor with throughput of one descriptor per 11.7 ms which significantly restricts the number of detected features by the real time applications. Feng-Cheng Huang et al proposed an architecture for SIFT feature extraction which is capable of feature detection on the images with the resolution of  $640 \times 480$  pixels in 3.4 ms and of the feature description in 0.03 ms per feature. However the article doesn't specify the utilized FPGA platform and it can be only roughly concluded that the design occupies 1.3 million logic gates.

The first published FPGA acceleration of SURF is [38]. Another implementation was proposed by Bouris et al [39]. They presented an implementation capable of processing the

images with the resolution of  $640 \times 480$  pixels at 56 frames per second. However they perform only the feature detection and orientation assignment and not the feature description. From their paper the number of processed features is also unclear. Another implementation was proposed by Battezzati et al in the article [40]. Their approach uses massive parallelization of the whole algorithm in two Xilinx Virtex-6 FPGAs achieving feature detection on the images with the resolution of  $640 \times 480$  pixels in 3.0 ms and the feature description in 0.01 ms per feature. However these results are achieved at the cost of extreme utilization of the FPGA fabric. Last known implementation of the FPGA SURF was proposed by Schaeferling et al [41]. Their Flex-SURF implementation is flexible in image size processing and features a specialized memory access management. The descriptors are computed in the embedded hardcore processor.

## 4 Method design

This chapter intends to provide the reader with the description of developed navigation algorithm. I originally had to follow up on the work done by Jan Šváb in his master thesis [4]. During his studies Jan Šváb developed an implementation of original SURF algorithm on FPGA and built a specialized hardware module suitable for the machine vision applications. However it has shown that his implementation was very consistent and in the hardware (FPGA configuration) part there is not much to improve. Partly because the FPGA fabric was almost all used by the original implementation. Partly because the hardware description language in which the implementation is written is almost impossible for reverse engineering. This is caused by the fact that this language is not interpreted by processor line by line but only specifies the dataflows through programmable logic which means all the actions are done in parallel. Room for improvement has shown to be in the software and in the minor improvements which make the minimodule more suitable for use as a self-contained navigation platform [10]. These improvements consisted in connecting auxiliary cores to the original design which perform control of the mobile robot, odometry reading and communication with the secure digital (SD) memory card.

Therefore I have developed a new algorithm for the image feature extraction specifically suitable for FPGA chips and realtime mobile robot navigation. In this chapter I would like to describe the algorithm and explain why I implemented the individual parts of the algorithm in a specific way. The algorithm consists of the image feature detection, the image feature description and own visual navigation. The image feature detection part is custom designed and it is highly optimized for use on the FPGA platform. In principle it is based on the original implementation but it is simplified so it can achieve the real time performance. The image feature description part uses BRIEF descriptor for description of interest points. The navigation algorithm is based on the SURFnav algorithm.

The first part of the chapter describes the architecture of FPGA chips which is necessary for definition of FPGA strengths and weaknesses. The second part describes the developed image feature detector. The third part is about used image feature descriptor and the last part is about the navigation algorithm.

## 4.1 Field-programmable gate array (FPGA)

The field-programmable gate array (FPGA) belongs to the family of semiconductor devices called Programmable logic devices (PLD). PLD is an electronic component used to build reconfigurable digital circuits. Unlike a logic gate, which has a fixed function, a PLD has an undefined function at the time of the manufacture. Before the PLD can be used it must be programmed.

FPGA contains the programmable logic components called Configurable logic blocks (CLBs) arranged in an array and a hierarchy of reconfigurable switches that can rearrange the interconnections between the logic blocks. Typical structure of this architecture is in

Figure 8: FPGA architecture.

Figure 8. Single CLB usually consists of a few logic cells. A typical cell consists of a configurable switch matrix with 4 or 6 inputs called Look-up table (LUT) which implements combinatorial logic, D-type flip-flop gate which implements sequential logic, full adder and some circuitry which determines global behaviour of the logic cell. Today's FPGAs can have up to several millions of logic cells.

Another important part of nowadays FPGA chips are clock management and generation circuitry (PLLs, DCMs), embedded memory blocks (block RAMs) and embedded multipliers. These components allow synthesizing designs with higher speed, clocking or memory demands. A recent trend is to incorporate traditional FPGAs with the embedded microprocessors and related peripherals to form a complete "system on a programmable chip". Therefore we can meet devices with integrated hardcore processors and various endpoints for high-speed communication buses (e.g. Ethernet, SATA, PCI Express). An example of such architecture is depicted in Figure 9 which shows the structure of Xilinx Virtex-5 family chip.

The FPGA configuration is generally specified using the hardware description language (HDL) or the schematic design. Programming the FPGA is very different from the classical programming. Classical program runs on a processor and it is interpreted line-by-line. In contrary to the FPGA programming where the code only specifies the dataflows through the FPGA fabric. But this actually gives the programmer the ability to develop a specialized and highly optimized design which can outperform almost any conventional design. Moreover this optimization usually leads to the possibility of using slower clock and therefore reduce the device's power consumption.

When the design is ready to be implemented on FPGA chip, using an electronic design automation tool, a technology-mapped netlist is generated. Netlist can then be fitted to

Figure 9: FPGA structure.

the actual FPGA architecture using the place-and-route process. It is also a good practice to write the simulation files for every design entity. It helps with the verification of design functionality and with the testing of the design for any unexpected situations.

The main drawbacks of the FPGAs are their cost and the time needed for development of an application. Compared with microprocessor designs FPGAs can offer true parallelism and the opportunity of designing fully custom and optimal designs. However learning to use or design complex FPGA systems is more challenging and also the debugging of the design is more difficult than by software approaches. Another issue is connected with the HDL programming because every developer uses his own coding style, making it almost impossible for reverse engineer of the code. This drawback can be partially suppressed by using and respecting the programming methodologies such as [42], [43].

## 4.2 Image feature detector

The image feature detector developed for purposes of this thesis is derived from original SURF detector (see chapter 3 for details) but it is highly optimized for the use on FPGAs. First of all I would like to present a closer look on SURF algorithm and comment the

individual parts from the view of FPGA programmer. I would like to provide the reader with the conclusions which lead me to implement the design the way I did.

## 4.2.1 Integral image generation

The whole algorithm starts with the generation of an integral image (see chapter 3 for details). The calculation of integral image is very simple and it is performed similarly on FPGA and in software. It consists of an array where the values of the integral image from previous image line are stored and of a sum register. The calculation is performed so that with every pixel the integral image value is calculated as a sum of value of sum register which sums luminance of pixels from the beginning of the image line, and a value of integral image of pixel right above the current pixel. The generation of integral image has only one issue. For example if we want to calculate an integral image of a picture with the resolution of  $1024 \times 768$  pixels in grayscale (8 bit per pixel) the integral image value binary representation can occupy 28 bits so the whole image occupies 3.5 times more memory than the original image. So if we don't want to lose any data, we need to dimension all the FPGA logic the way it can handle such numbers. This consequently leads to higher utilization of the FPGA fabric. Another problem with integral image is its storage. Despite the modern FPGAs incorporate embedded block RAMs the size of an integral image on standard resolution frame can't be stored in the device. To my best knowledge there are two implementations of SURF algorithm on FPGA which rely on storing an image in embedded block RAMs. Bouris et al [39] presented an implementation which can process images with resolution only up to  $640 \times 480$  pixels where the integral image storage occupies 72% of block RAM resources in the Xilinx Virtex-5 device. Battezzati et al [40] presented a short paper on the SURF architecture which also relies on storing the integral image data inside the FPGA. Their solution occupies 90% of two high-end Xilinx Virtex-6 FPGAs. Based on the above it is obvious that for the price of higher speed extreme utilization of FPGA fabric needs to be paid.

### 4.2.2 Hessian detector

In software the contribution of integral image is undeniable. As it was mentioned in chapter 3 it is necessary to perform only four read operations in order to calculate the rectangular area integral of any size. This feature is mostly utilized by Hessian point detector. It significantly helps to speed up the convolution of an image with the appropriate Gaussian kernels. Considering the size and number of these kernels it would take much more time to make the convolution pixel by pixel. This is partly due the processors sequential nature. On the other side the FPGA can utilize parallel logic so it should be possible to do the convolution "on-line". This would mean buffering only enough data, to be able to calculate the appropriate responses of Gaussian kernels. But if we take a closer look it would be impossible to actually calculate the responses. The smallest Gaussian kernel in original implementation is of  $9 \times 9$  pixels size and features 126 weighted pixels (for

all kernels  $D_{xx}, D_{yy}, D_{xy}$ ). It would eat up an enormous portion of FPGA fabric to perform the sum of these weighted elements reliably and fast. With such an utilization the scale space construction wouldn't be even possible.

This leads to an idea of simplifying the Gaussian kernels. In my algorithm the Gaussian kernels are replaced with three point central numerical second order differences [44]. Equations 5, 6 and 7 show numerically calculated second order partial differences of two dimensional function at the point x, y where h is a stepping distance.

$$\frac{\partial^2 f(x,y)}{\partial x^2} = \frac{f(x+h,y) - 2f(x,y) + f(x-h,y)}{h^2}$$

(5)

$$\frac{\partial^2 f(x,y)}{\partial y^2} = \frac{f(x,y+h) - 2f(x,y) + f(x,y-h)}{h^2}$$

(6)

$$\frac{\partial^2 f(x,y)}{\partial x \partial y} = \frac{f(x+h,y+h) + f(x-h,y-h) - f(x+h,y-h) - f(x-h,y+h)}{4h^2}$$

(7)

After convolution with the simplified kernels the data are processed by Hessian detector. As an original SURF algorithm, my implementation uses the determinants of Hessian matrices to locate the image's significant points. The determinants are calculated exactly by definition described by the equation 4 in chapter 3.

#### 4.2.3 Scale space construction

The size of convolution kernels is closely related with the scale space construction. The scale space can be constructed in two different ways. The first one is to scale dimensions of convolution kernels and perform convolution on fixed image. This way is used by the original SURF algorithm because due to the use of an integral image it takes same time to compute the response of convolution kernel of any size. The second one is to iteratively smooth and subsample the original image with the fixed size of convolution kernels. My algorithm uses the second way of constructing the scale space. The reason is in the implementation of the algorithm in FPGA fabric.

As it has been shown thanks to simplifying the convolution kernels and lack of usability of an integral image in further stages of the navigation algorithm the integral image generation has been omitted. The image feature detector was developed as on-line from the beginning. This means that it processes the data stream of any source directly. With convolution kernel of  $3\times3$  pixels size on base scale it is only necessary to buffer 3 consecutive image lines. After that, with every incoming pixel the kernels produce the result of convolution with underlying 9 pixels for further processing by Hessian calculator (the whole architecture is described and depicted in chapter 5). The architecture of image feature detector is divided into the separate processing chains, each detecting features on separate scale. Each chain takes pixel data on the input and in the first stage buffers 3 lines of them and produces the rescaled pixel data and the convolution data for further processing.

Figure 10: Comparison of convolution kernels.

These rescaled data are connected on the input of another processing chain. It can be said that the scale space construction is only a residual product of buffering three lines of pixel data which is necessary. So far the four scales are implemented in the hardware with scale factor of two. This corresponds to convolution with kernels of sizes  $3\times3$ ,  $6\times6$ ,  $12\times12$  and  $24\times24$  pixels. The reason is in the implementation because it is more economical to use the division by powers of two (in this case the sum of four pixels is divided by four) than to divide by any other number. However it is possible to divide by any number but it would take more FPGA fabric to do so. In Figure 10 there is a comparison of convolution kernels of the same size from the original implementation and my implementation. The original implementation kernels are in the first row, the simplified kernels are in the second row. By  $D_{xx}$  and  $D_{yy}$  kernels black squares represent the weighting of each image pixel by coefficient -2. By  $D_{xy}$  black squares represent the weighting of each image pixel by coefficient -1. White squares represent weighting coefficient 1 and gray squares 0. It can be seen that besides the  $D_{xy}$  kernel there is not a significant difference.

### 4.2.4 Interest point localization

The next step is to locate the local maxima amongst Hessian values. This is done by comparing Hessian value with its eight closest neighbours. In order to achieve this three lines of Hessians need to be buffered and after that processed simultaneously. After locating the local maxima these are compared with the pre-defined threshold to produce the final localization of interest points. In further stage of implementation these points could be simply compared throughout the scale space in order to obtain the highest local maxima amongst all located features but this functionality has not yet been implemented.

## 4.3 Image feature descriptor

I chose the BRIEF descriptor (see chapter 3 for details) for my work because it had shown that on a long term navigation scenario dataset it outperformed other feature descriptors in speed and repeatability [6]. The BRIEF descriptor uses intensity comparison of pixels inside an image patch which surrounds located feature. These comparisons form a set of unique binary tests which are subsequently stored into an  $n_d$  bit vector. In original paper the  $n_d$  constant takes values of 128, 256 and 512. For my work I decided to implement 128 bit long BRIEF descriptor on the patch of size  $50 \times 50$  pixels. The composition of unique binary tests has been generated randomly.

### 4.3.1 Descriptor generation

The generation of BRIEF is completely done in FPGA fabric. There is an implementation of BRIEF descriptor in the OpenCV library which uses an integral image to compute the descriptor. This is logical since the features are normally detected on several scales and therefore the patch and consecutively the pixel sizes need to be properly enlarged. But my implementation doesn't feature integral image generation and storage therefore the descriptor needs to be calculated in another way. Descriptor calculation is done from the original image which is stored in an external memory. If I save only the original image, it would take a lot of memory read operations to calculate descriptors on higher scales. Therefore the algorithm saves the original image together with its smoothed and subsampled copies. Table 1 shows the performance comparison of description based on the integral image, the original image and the original image with all the scales saved in the memory. Values in the table are derived from computing necessary data for image with the resolution of  $1024 \times 768$ pixels. The overall size in the memory is calculated as a number of pixels times bit width. This bit width is 8 bit per pixel for the original and the rescaled images and 28 bit per pixel for the integral image. The entry of number of write operations assumes a fully utilized 32 bit wide memory bus to an external memory. Number of read operations expresses an amount of memory read operations which are necessary for calculation of one 128 bit wide BRIEF descriptor on an appropriate scale. For the integral image and the original image with all scales this amount is constant. For the original image saved in the memory it is necessary to perform four times more read operations to calculate the descriptor with the every following scale. Table 1 shows that when operating only on four scales it is most efficient to buffer the image data for all of the scales. The precise implementation is described further in the chapter 5.

### 4.3.2 Orientation assignment

By the computer vision algorithms it is usual to perform orientation assignment of the descriptor so the interest point description is immune to rotation changes. This is necessary for computer vision applications like image stitching or object recognition where there is

|                            | Integral image              | Original image      | Original image<br>with scales |

|----------------------------|-----------------------------|---------------------|-------------------------------|

| Size in the memory         | $22 \ 020 \ 096 \mathrm{b}$ | $6\ 291\ 456b$      | 8 454 144b                    |

| Number of write operations | $688 \ 128$                 | 196  608            | 264  192                      |

| Number of read operations  | 1024                        | 256/1024/4096/16384 | 256                           |

Table 1: Description performance comparison.

high possibility of a bigger viewpoint change. However for purposes of the mobile robotics the orientation assignment of the descriptor is not necessary. When using ground vehicles the camera is usually mounted on top of the mobile robot and aims forward. When not operating in extremely rough terrains the vertical axis of the camera remains still.

## 4.4 Navigation algorithm

The navigation algorithm is based on the SURFnav algorithm [11], [3], [1] briefly described in the chapter 2. Now the algorithm will be described in more detail together with proposed modifications. The algorithm consists of two main phases the teach phase and the repeat phase.

## 4.4.1 Teach phase

During the teach phase the mobile robot is guided through the environment along the polyline path. The polyline path is split into individual line segments creating the landmark map of the environment. The algorithm uses the fact that when traversing the line segment with camera heading forward the detected image features are migrating through the image along the imaginary lines from the center of the image to the edges. Making the path a virtual tunnel of image features. The local segment landmark map contains information about in which part of the segment the image features were visible and what were their image coordinates. This information is sufficient to compute image coordinates of the landmarks for particular robot position. The landmark map is composed from entries which structure can be seen in the table 2. In my implementation the image feature positions are integer values and they are described by the BRIEF descriptor.

## 4.4.2 Repeat phase

The repeat phase of the algorithm navigate the mobile robot along the individual segments of the composed map. At the beginning of each segment the mobile robot turns to the predefined direction by means of odometry and starts traversing the segment. During

| Record                           | Value                         |

|----------------------------------|-------------------------------|

| Initial azimuth and length:      | 2.13, 7.03                    |

| Landmark 0:                      |                               |

| First position:                  | 760, 163                      |

| Last position:                   | 894, 54                       |

| First and last visible distance: | 0.00, 4.25                    |

| Descriptor:                      | 1, 11010110001010001011101001 |

| Landmark 1:                      |                               |

| First position:                  | 593, 381                      |

| Last position:                   | 689, 377                      |

| First and last visible distance: | 0.72,  6.73                   |

| Descriptor:                      | -1, 0100100011100110111001110 |

Table 2: Segment landmark map composition.

the traversal the system detects image features and match them with the learned ones. Figure 3b in chapter 2 shows the situation from the mobile robot's point of view. The red circles in the figure highlight image features which are searched in a current view. The position of the red dashed line is determined by the means of odometry. If the match between keypoints is detected the difference between observed and expected position of image feature in the image is calculated. The differences are used to create navigation histogram with fixed number of bins. The maximum peak in the histogram determines the correction of heading of the mobile robot.

Figure 11: Detected landmarks in the picture and the corresponding navigation histogram.

Figure 11 shows the typical result of visual compass. Blue crosses mark currently visible image features and green crosses corresponds to landmarks stored in the map. Matched landmarks are connected with the lines. Correspondences near the center value are connected with green lines, others are connected with the blue ones. The navigation histogram is depicted under the picture showing that the mobile robot is slightly left from the pre-learned trajectory.

## 5 Implementation

In the previous chapter the theoretical basis for implementation is described. This chapter describes the actual implementation of the algorithm in hardware (FPGA configuration) and software. The first part of this chapter provides the reader with an overview of reference boards on which the implementation has been tested. The second part discusses the proposed FPGA architecture and the last part is about the implementation of SURFnav navigation algorithm in the software of the module.

Due to the necessity of previous theoretical testing of the detection and description algorithm an implementation in MathWorks Matlab software was also developed. The actual implementation has been developed in Xilinx ISE Design Suite System Edition [45]. The ISE Design Suite System Edition includes ISE Design Software(XISE), Xilinx Platform Studio(XPS), Software Development Kit(SDK) and System Generator for DSP. The ISE Design software is the main application of the suite. It is the project manager, text and schematic editor. It allows the user to built custom FPGA designs by means of HDL programming, schematic drawing or by adding macro components from various libraries to the design. Xilinx Platform Studio is used for creating the whole System On a Programmable Chip (SOPC) designs by adding and connecting components from the vast database of embedded Intelectual Property(IP) cores. It also allows the user to built the new IP cores by providing the assisted design flow. Both XPS and XISE are intended to built the FPGA configuration and provide the user with the resulting bitstream. Xilinx Software Development Kit provides programming environment for designs which features embedded processors. It allows to built and compile software projects which can be then run on FPGA specific processor architecture (softcore or hardcore).

(a) Schvab minimodule

(b) Xilinx ML507 board

Figure 12: Development platforms.

## 5.1 Reference boards

For the purposes of algorithm evaluation two development boards featuring same FPGA chip have been chosen. The first of them is a Schvab minimodule, built by Jan Šváb [4], [10]. The minimodule composes of a standard off-the shelf Avnet AES-MMP-V5FXT70-G Mini-Module Plus board and a custom baseboard specifically designed for computer vision applications. Figure 12a shows the minimodule with the connected heathsink over the FPGA chip.

The second one is a Xilinx ML507 evaluation platform board. This is a high-end development board which features a lot of auxiliary circuitry. Figure 12b shows the layout of the development board. In the table 3 the main features of both boards are listed. By the ML507 development board only circuitry which was utilized during the development of this thesis is listed.

|                          | Schvab minimodule                                                                                                                          | ML507 development board                                                                                                                     |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA                     | Xilinx Virtex-5<br>XC5VFX70T-2-FF665                                                                                                       | Xilinx Virtex-5<br>XC5VFX70T-1-FFG1136                                                                                                      |

| Memory                   | 64MB DDR2 SDRAM<br>32MB flash memory<br>4MB SSRAM<br>SD Card slot                                                                          | 256MB DDR2 SDRAM<br>32MB flash memory<br>1.125MB ZBT synchronous SRAM<br>SD Card slot                                                       |

| I/O and<br>Communication | serial port<br>USB 2.0 PHY<br>10/100/1000 Ethernet PHY<br>SATA master/slave subsystem<br>Expansion connector (23 pins)<br>Camera connector | RS232 serial port<br>Video input (VGA)<br>Video output (DVI connector)<br>LEDs, DIP switches, Push buttons<br>Expansion connector (96 pins) |

Table 3: Reference boards features.

## 5.2 FPGA configuration

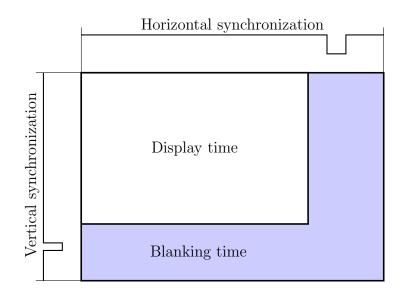

From the beginning of my bachelor project I set up a goal to develop an implementation which can operate in real time. This means that all image features with corresponding descriptors are calculated within the duration of one image frame. One image frame is defined as a duration of full frame with digital video signal timing specifications. Digital video signal consists of two main areas. Display area, where image pixel data are provided, and blanking area, where there are no pixel data provided (corresponds to black color). This is due to the historical development because the cathode ray tube (CRT) monitors

which compose picture on the screen by beam deflection need some time to move the beam from the end of one line to the beginning of the next line. For precise synchronization horizontal and vertical synchronization pulses are provided. For standardized 4:3 resolutions the display area forms about 70% of the whole frame. In Figure 13 there is a digital video timing diagram showing both display and blanking area of the image and corresponding synchronization signals.

Figure 13: Digital video timing diagram.

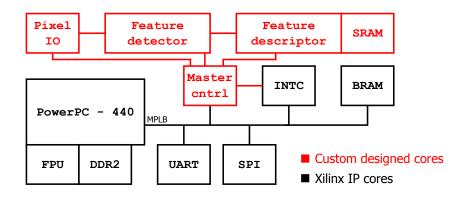

In Figure 14 there is an overview of the proposed FPGA architecture. The design is divided into four main parts: pixel I/O, feature detector, feature descriptor and embedded processor with its peripherals. Pixel I/O part comprises of several cores, which purpose is to provide further logic with pixel data and corresponding data-aligned clock signals together with the signals determining position in the image. Feature detector takes the stream of pixel data on the input and provides locations of image features on the output. Feature descriptor part of the design takes positions of located features and calculates corresponding descriptors. The Feature descriptor part utilizes the memory interface with the on-board SRAM memory which has shown to be the key component in feature description process. Both the Feature detector and descriptor parts are custom designed and completely standalone. They form a complete feature extractor which takes the image data on the input and provide locations of key features together with their description on the output. The last part in the design features embedded processor core with peripherals. These peripherals are except one communication core all Xilinx's IP cores. The Embedded processor part is used for the actual visual navigation algorithm. Now every part of the design will be presented in detail.

Figure 14: Block diagram of the high-level FPGA architecture.

## 5.2.1 Pixel I/O

The reference board Xilinx ML507 features VGA in and DVI out circuitry making it possible to connect the board with VGA output of the computer on one side and with the display on the other side. This is a very useful feature for development of computer vision algorithms. Thanks to this feature the programmer can instantly verify functionality of the solution only by sight. Thorough testing can be performed later but for basic check it provides an excellent help. Pixel I/O comprises of three individual cores: I2C\_CNTRL, VGA\_COUNTER and VGA\_CNTRL.

I2C\_CNTRL core is a simple core which performs initialization of on board chips connected to the VGA input and DVI output by means of i<sup>2</sup>c serial bus in order to assure their correct functionality.

By VGA input chip (Analog Devices AD9980 High Performance 8-Bit Display Interface chip) the initialization consists of setting correctly registry information about incoming VGA signal. This helps the device to correctly synchronize with the incoming analog data signal and provide clear and stable image and pixel clock for further processing in FPGA fabric. It also provides the horizontal and vertical synchronization signals, which all together form an external input of the whole implementation. By DVI output chip (Chrontel CH7301C) the initialization consists of master enable of the chip functionality and provision of information about incoming data signal (from FPGA).

The protocol for communication with both devices is a standard  $i^2c$  protocol without acknowledging. As has been said this core is used only for initialization of auxiliary circuitry after start (or restart) therefore there is no need for implementing the whole  $i^2c$  communication interface. This core is suitable to perform initialization of almost any  $i^2c$  or  $i^2c$ -like device, such as camera module (OmniVision OV9653 CMOS camera) attached to the Schvab minimodule board.

- VGA\_COUNTER core is a second key component on the input of the design. It's purpose is to synchronize with the incoming horizontal and vertical pulses and provide the logic with x,y coordinates of the right incoming pixel data. Together with x,y coordinates there is one more output from the core which marks the display and blanking area of the image.

- VGA\_CNTRL core is an auxiliary output core which helps graphically represent any debugging data from the FPGA logic. Moreover it can read the content of SRAM memory which is used for storing the image data. It forms something like a presentation layer to the DVI output chip, rearranging the data to match the correct timing and format for displaying.

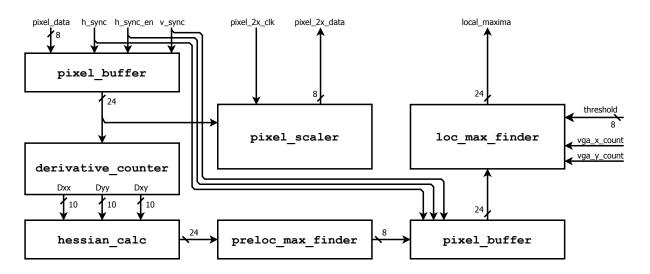

#### 5.2.2 Feature detector

Feature detector is a system of heavily pipelined cores which are divided into four separate feature detection processing chains, each processing the image on a different scale. Feature detection processing chain takes 8 bit wide pixel data stream on the input, calculates determinants of Hessian matrix and locates the local maxima amongst them. There are seven cores in the design of the feature detection processing chain, each of them represented by an VHDL entity. The interconnection of individual entities is shown in Figure 15 (for better readability clock and reset signals are not depicted because they are connected to all of the cores). The processing chain works as follows.

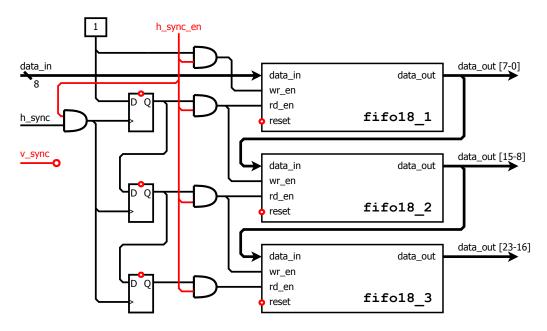

First of all three lines of pixel data are buffered in the PIXEL\_BUFFER core. This core stores incoming image data in local block RAM resources and release them in appropriate

Figure 15: Feature detection chain architecture.

moment. It means that with every incoming pixel the core provides the luminance data for three pixels located in the image above each other.