Master thesis

Czech Technical University in Prague

Faculty of Electrical Engineering Department of Systems and Control

# FPGA-based support for predictable execution model in multi-core CPU

Bc. Maxim Baryshnikov

Supervisor: Ing. Michal Sojka, Ph.D. Field of study: Cybernetics and Robotics Subfield: Common Cybernetics and Robotics May 2018

# **Acknowledgements**

I would first like to thank my thesis advisor Ing. Michal Sojka, Ph.D., for his assistance and dedicated involvement in every step throughout the process. Without his great mentorship this work would have never been accomplished. I would also like to thank my family and friends for their great moral support.

# Declaration

I hereby declare that I have completed this thesis with the topic "FPGA-based support for predictable execution model in multi-core CPU" independently and that I have included a full list of used references.

Prague, May \_, 2018

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

V Praze, \_\_. května 2018

# Abstract

In attempts to make real-time embedded systems less expensive and more powerful, researchers in the field are working on ways to incorporate Commercial-off-theshelf (COTS) multicore devices into safety-critical designs. The Predictable Execution Model (PREM) is a promising solution to overcome the problems of shared resources interferences on such multicore platforms. One of an existing implementation of PREM employs hypervisor-based memory access monitor. It has overheads, which could be reduced with the use of FPGA-based PREM memory access monitor instead. The aim of this thesis is to implement such solution and prove the efficiency of it comparing to the hypervisor-based one.

The stated PREM watchdog was successfully implemented on Xilinx Zynq Ultrascale+ MPSoC platform using the abilities of ARM's CoreSight Debug & Trace system. The results show that in case of using FPGA-based memory watchdog maintenance takes 2.88 times less than the hypervisor-based solution requires in average (the hypercall time). Hence, the statement that HW-based guard may decrease the overhead of PREM application when compared to the software-based guard is proven.

**Keywords:** predictable execution, Xilinx Zynq Ultrascale+, MPSoC, FPGA, tracing, memory, PREM

Supervisor: Ing. Michal Sojka, Ph.D.

# Abstrakt

Z důvodu potřeby snížení nákladů a zvýšení výkonu embedded real-time systémů, pracují vědci po celém světě na způsobech, jak přizpůsobit hotová komerční zařízení bezpečnostně-kritickému designu. Předvídatelný exekuční model je slibné řešení k překonání problémů s interference na sdílených zdrojů na více jádrových platformách. Jedna z již existujících implementací PREM zahrnuje sledování přístupů do paměti založeny na hypervizoru. Problémy, které taková implementace vytváří (overheady v sledovaném softwaru) je možno minimalizovat využitím FPGA založeném na PREM. Cílem této práce je implementace popisovaného řešení a ověřené efektivnosti v porovnání s řešením založeném na hypervisoru.

Uvedeny PREM watchdog byl úspěšně implementován na platformě Xilinx Zynq Ultrascale+ MPSoC využitím moznosti trasovacího frameworku CoreSight. Výsledky ukazuji že v případě použiti uvedeného watchdogu založeného na FPGA, trvají přístupy 2.88 krát menší dobu než přístupy k hypervizoru pomoci hypercallu. Tímto se tvrzeni, ze hardwarová implementace watchdogu může snížit overhead potvrdilo.

Klíčová slova: Xilinx Zynq Ultrascale+, PREM, MPSoC, FPGA, trasování, ARM

# Contents

| Project Specification                                              | 1   |

|--------------------------------------------------------------------|-----|

| 1 Introduction                                                     | 3   |

| <b>2</b> Theoretical Background<br>2.1 Predictable Execution Model | 5   |

| (PREM)                                                             | 5   |

| 2.2 State of the Art                                               | 6   |

| 2.3 The Problem Statement                                          | 8   |

| 3 Hardware Platform Overview                                       | 11  |

| 3.1 Zynq MPSoC's capabilities                                      | 11  |

| 3.1.1 Zynq MPSoC Overview                                          | 11  |

| 3.1.2 Tracing capabilities                                         | 13  |

| 3.2 ARM's CoreSight Framework                                      | 14  |

| 3.2.1 Trace Sources                                                | 16  |

| 3.2.2 Trace Links and Sinks                                        | 20  |

| 3.2.3 Embedded Cross-Trigger                                       | 21  |

| 3.3 ARM's Performance Monitoring                                   | 0.0 |

| Unit                                                               | 23  |

| 4 PREM Watchdog                                                    |     |

| Implementation                                                     | 25  |

| 4.1 Concept                                                        | 25  |

| 4.2 CoreSight System Configuration                                 | 26  |

| 4.3 Programmable Logic Design                                      | 28  |

| 4.4 Event Masking Problem                                          | 30  |

| 4.5 PL Logic Driver API                                            | 32  |

| 5 Performance Evaluation                                           | 33  |

| 5.1 Precision evaluation                                           | 33  |

| 5.2 Comparison with software-only                                  |     |

| watchdog                                                           | 34  |

| 6 Conclusion                                                       | 37  |

| A Bibliography                                                     | 39  |

# **Figures**

| 2.1 An example of PREM schedule.                                         |  |

|--------------------------------------------------------------------------|--|

| Source: $[PBB^+11]$                                                      |  |

| 2.2 Real-Time I/O Management                                             |  |

| System proposed by R. Pellizzoni et<br>al. Source: [PBB <sup>+</sup> 11] |  |

| 2.3 An ADAS-like scenario schedule                                       |  |

| presented as direct acyclic graph. In                                    |  |

| green: compatible intervals. In white:                                   |  |

| computation phases. In read:                                             |  |

| memory access phases. Source:                                            |  |

| [MFS <sup>+</sup> 18]                                                    |  |

| 2.4 Gantt diagram of schedule depicted                                   |  |

| in Figure 2.3 of PREM intervals                                          |  |

| among multiple CPUs. The green                                           |  |

| ones depict computation phases. The                                      |  |

| read ones are memory access phases.                                      |  |

| Source: $[MFS^+18]$                                                      |  |

| 2.5 HERCULES Memory access                                               |  |

| scheduling & supervision. Source:                                        |  |

| [MSH17] 8                                                                |  |

|                                                                          |  |

| 3.1 Zynq UltraScale+ MPSoC                                               |  |

| Top-Level Block Diagram. Source:                                         |  |

| [Incc] 12                                                                |  |

| 3.2 Zynq UltraScale+ MPSoC                                               |  |

| Top-Level AXI Interconnect                                               |  |

| Architecture. Source: [Incc] 13                                          |  |

| 3.3 Zynq UltraScale+ MPSoC Debug                                         |  |

| Block Diagram. Source: [Incc] 15                                         |  |

| 3.4 ETM's resource selection overview.                                   |  |

| Source: [Lime] 18                                                        |  |

| 3.5 The necessary option setup in                                        |  |

| FreeRTOS BSP for enabling STM<br>tracing in Xilinx SDK IDE 19            |  |

| tracing in Xilinx SDK IDE 19<br>3.6 FreeRTOS tracing in Xilinx SDK       |  |

| IDE                                                                      |  |

| 3.7 Funnel block diagram. Source:                                        |  |

| [Limc]                                                                   |  |

| 3.8 ECT block diagram. "The CTI at                                       |  |

| the top is configured to propagate                                       |  |

| the trigger event on Trigger Input 0                                     |  |

| to Channel 0." Source: [UXSCT] 21                                        |  |

| 3.9 CTI internal logic overview.                                         |  |

| Source: [Lima]                                                           |  |

|                                                                          |  |

| 4.1 The implementation concept                                           |  |

| overview                                                                 |  |

| 4.2 ETM's configuration              | 28 |

|--------------------------------------|----|

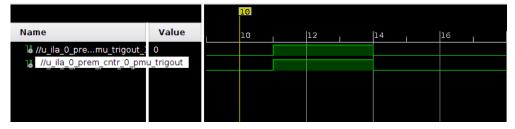

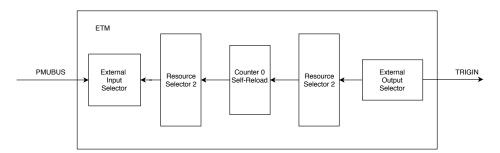

| 4.3 The measured time of the Trigger |    |

| acknowledgment. The sampling         |    |

| period is 10 ns                      | 31 |

| 4.4 The modified ETM's configuration | 1  |

| concept overview                     | 31 |

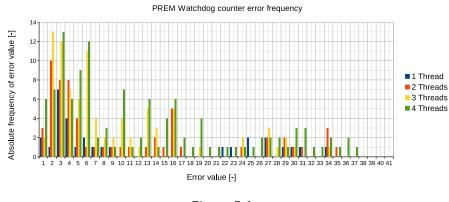

| 5.1                                  | 34 |

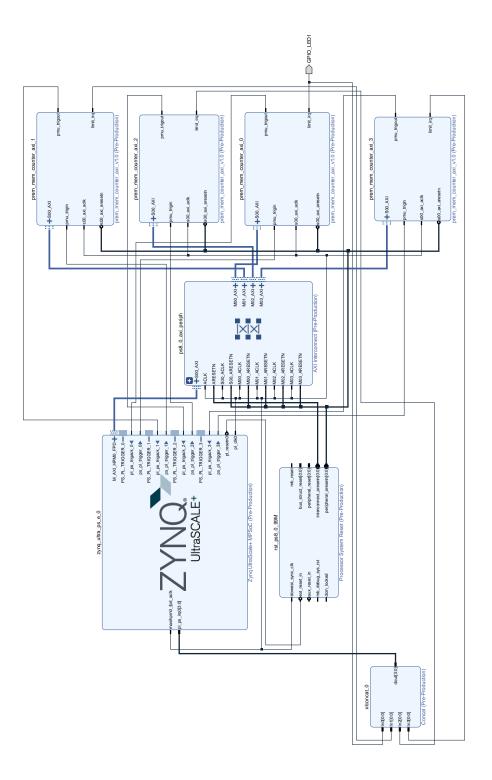

| A.1 The complete PL design           | 42 |

| A.2 The PL logic concept             | 43 |

# **Tables**

| 4.1 PREM  | Watchdog registers  |    |

|-----------|---------------------|----|

| overview. | All are 32-bit wide | 30 |

|           |                     |    |

5.1 The comparison of PL Watchdog with hypervisor watchdog. ..... 35

# ZADÁNÍ DIPLOMOVÉ PRÁCE

# I. OSOBNÍ A STUDIJNÍ ÚDAJE

|     | Příjmení:        | Baryshnikov                   | Jméno: Maxim | Osobní číslo: 420064 |

|-----|------------------|-------------------------------|--------------|----------------------|

|     | Fakulta/ústav:   | Fakulta elektrotechnická      |              |                      |

|     | Zadávající kated | ra/ústav: Katedra řídicí tech | niky         |                      |

|     | Studijní program | : Kybernetika a robotika      |              |                      |

|     | Studijní obor:   | Kybernetika a robotika        |              | J                    |

| II. | ÚDAJE K DIPL     | OMOVÉ PRÁCI                   |              |                      |

Název diplomové práce:

Hardwarová podpora předvídatelné exekuce na vícejádrových procesorech

Název diplomové práce anglicky:

FPGA-based support for predictable execution model in multi-core CPU

Pokyny pro vypracování:

Seznam doporučené literatury:

[1] Xilinx, Zynq UltraScale+ MPSoC, Technical Reference Manual

[2] R. Pellizzoni et al., 'A Predictable Execution Model for COTS-Based Embedded Systems,' 2011 17th IEEE Real-Time and Embedded Technology and Applications Symposium, Chicago, IL, 2011, pp. 269-279.

Jméno a pracoviště vedoucí(ho) diplomové práce:

Ing. Michal Sojka, Ph.D., katedra řídicí techniky FEL

Jméno a pracoviště druhé(ho) vedoucí(ho) nebo konzultanta(ky) diplomové práce:

Datum zadání diplomové práce: 30.01.2018

Termín odevzdání diplomové práce: 25.05.2018

Platnost zadání diplomové práce: 30.09.2019

Ing. Michal Sojka, Ph.D. podpis vedoucí(ho) práce

prof. Ing. Michael Šebek, DrSc. podpis vedoucí(ho) ústavu/katedry prof. Ing. Pavel Ripka, CSc. podpis děkana(ky)

### III. PŘEVZETÍ ZADÁNÍ

Diplomant bere na vědomí, že je povinen vypracovat diplomovou práci samostatně, bez cizí pomoci, s výjimkou poskytnutých konzultací. Seznam použité literatury, jiných pramenů a jmen konzultantů je třeba uvést v diplomové práci.

Datum převzetí zadání

Podpis studenta

# Chapter 1 Introduction

Today's Automotive and Avionics industrial demands are suffering from the need for high-performance hardware to be incorporated in safety-critical systems. For example, Advanced Driver Assistant and Autopilot systems require powerful Graphics Processing Units for real-time environment tracking algorithms. Generally, the use of parallel algorithms in that field introduces many benefits in the sense of performance.

In attempts to make real-time embedded systems less expensive and more computationally powerful, a majority of researchers in the field are working on ways to incorporate Commercial-off-the-shelf (COTS) devices into safety-critical designs. One of the significant problems arising, while using a multi-core COTS hardware in real-time applications is the enormous unpredictability of shared resources competition. For instance, a common System-on-Chip (SoC) could contain CPUs, GPUs, and FPGAs all sharing the same interconnect and memory hierarchy, which leads to unwanted interferences. Thus, COTS devices cannot be used in systems with tightly deterministic time constraints without applying some third-party arbiters to the parts of a system where those shared resources present.

The European Project HERCULES<sup>1</sup>, where CTU participates, uses Predictable Execution Model (PREM) [PBB<sup>+</sup>11] in their automotive software stack. Their solution also includes a software-based guard that monitors the program execution in order to limit potential interference to other parts of the system. The monitoring ensures that the given time and memory budgets do not overrun but also introduces some overhead. The use of hardware-based guard instead may reduce the overheads that the software-based solution have. This thesis aims to prove that concept of hardware-based execution monitoring.

The thesis is structured as follows: Chapter 2 of this work is dedicated to the theoretical introduction into PREM's problematic. The main concepts and terms, which are used in the rest of this thesis are defined there.

<sup>&</sup>lt;sup>1</sup>http://hercules2020.eu/

#### 1. Introduction

Chapter 3 introduces the reader to Xilinx Zynq Ultrascale+ platform and its abilities, focusing on hardware tracing capabilities. Xilinx Zynq Ultra-Scale+ MPSoC ZCU102 Evaluation Kit was given as a hardware platform for this work. Due to the general complexity and vast variety of features this platform provides, the investigation of it has taken the vast majority of the time spent on this project. This is the reason why Chapter 2 provides the information about features that were not applied in the final solution. However, those unemployed findings may serve well for future work purposes, and that is why they are kept there.

Chapter 4 explains the PREM Watchdog's implementation in details both from software part and hardware (FPGA) part points of view. The chapter aims to reason about the decisions that were made and about an implementation concept. Furthermore, it discusses the problems that were met on the way.

Finally, Chapter 5 describes the tests of developed functionality and overhead comparison with the software-based solution. The results are discussed in Conclusion.

# Chapter 2

# **Theoretical Background**

The following chapter provides some general explanation of the terms and concepts about the stated topic (Section 2.1). In Section 2.2, there is an overview of already implemented solutions. Finally, the part of the problem which this work aims to solve is discussed (Section 2.3).

### 2.1 Predictable Execution Model (PREM)

Predictable Execution model (PREM), proposed by Pellizzoni et al. [PBB<sup>+</sup>11], is a way to execute safety-critical software in deterministic time on multicore systems. The primary target of struggle on such systems is cache misses while their amount strongly affects the worst-case execution time (WCET) with its indeterminism. PREM solves the mentioned issues by applying resource access scheduling on a given program. A program should have execution intervals which are stated either as **predictable** or **compatible**. Predictable intervals "are executed *predictably* and *without cache misses*" [PBB<sup>+</sup>11], and cannot be preempted until the end of scheduling interval. Predictable intervals are then divided into sub-phases which are the following:

- Cache Prefetch

- Computations

- Cache Write-Back

During the cache **prefetch** phase, all the instructions and data needed for the computing stage are loaded into the cache which is shared among all cores. It is essential to avoid *self-eviction* of the cache, i.e., prefetching of the cache line does not rewrite the data fetched in the same phase. Then follows the **computation** phase where no cache misses could occur because all needed data are already there. Finally, after the computation is done the CPU posts the results back to the cache during the **write-back** phase.

Compatible intervals may follow after a sequence of predictable intervals. The task running in it is allowed to be preempted and have cache misses. It can not, however, block the execution indefinitely. For that reason, communication with peripheral devices should be restricted as much as possible during this phase.

The transformation of legacy code to PREM-compatible program requires a programmer to put pragmas (e.g., **predictable** code blocks, as stated in [PBB<sup>+</sup>11]) which define single predictable intervals of a program and its limitations (e.g., time and memory budget). PREM real-time compiler should then put prefetch and write-back instructions at the beginning and the end of a predictable interval.

The intervals are then scheduled either on-line or off-line such that the memory access resource is shared between CPU and I/O peripherals exclusively during the non-preemptive intervals.

### 2.2 State of the Art

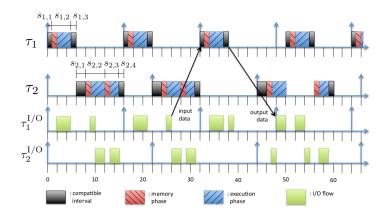

In the original paper ([PBB<sup>+</sup>11]) which introduced PREM, the authors implement the single-core approach that is primarily focused on efficient and safe I/O peripherals distribution among tasks that are executed on CPU periodically. Figure 2.1 depicts an example of such schedule where memory access resource is shared exclusively between tasks  $\tau_1$  and  $\tau_2$  that do some computations and tasks  $\tau_1^{I/O}$  and  $\tau_2^{I/O}$  that work with I/O flows.

Figure 2.1: An example of PREM schedule. Source: [PBB+11]

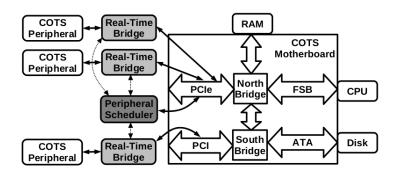

To achieve the PREM synchronization of I/O devices, R. Pellizzoni et al. introduce FPGA-based *real-time bridge* and *peripheral scheduler*. Figure 2.2 shows the hardware layout they used. It does not, however, cover multiple CPU setups. The further research focused more on incorporating PREM with multicore systems without the need of hardware-based arbiter, introducing the concept of multithreaded PREM scheduling based on fork-join principle [AP14]. Based on this and other works, J. Matějka et al. introduced

**Figure 2.2:** Real-Time I/O Management System proposed by R. Pellizzoni et al. Source: [PBB<sup>+</sup>11]

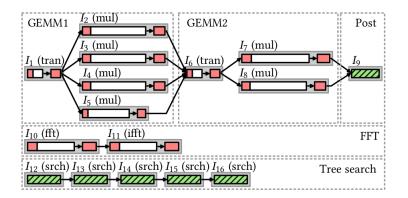

a complete PREM toolchain [MFS<sup>+</sup>18] consisting of a compiler for ARM and scheduling model which was successfully evaluated on Advanced-Driver Assistant-System (ADAS) scenarios (refer to Figure 2.3 and Figure 2.4).

**Figure 2.3:** An ADAS-like scenario schedule presented as direct acyclic graph. In green: compatible intervals. In white: computation phases. In read: memory access phases. Source: [MFS<sup>+</sup>18]

**Figure 2.4:** Gantt diagram of schedule depicted in Figure 2.3 of PREM intervals among multiple CPUs. The green ones depict computation phases. The read ones are memory access phases. Source: [MFS<sup>+</sup>18]

HERCULES project [Pro] also considers applying PREM in similar manner as proposed in [MFS<sup>+</sup>18] to achieve predictive execution of their ADAS framework on multicore systems. However, instead of using real-time bridges as [PBB<sup>+</sup>11] proposes they run that logic in a software arbiter such as VM or hypervisor, so they do not need to integrate additional hardware on a SoC.  $[BBC^+17]$

### 2.3 The Problem Statement

As it was mentioned in the section, the HERCULES framework solution uses a hypervisor to drive PREM application's execution. In particular, it must be in charge of two tasks:

- Scheduling of execution intervals and phases

- Detecting misbehaving applications

The detection of the faulty behavior for a safety-critical program is unconditionally required. Not only due to an axiom that every software may have a bug but also because of safety-related certification process which every piece of control system's software should pass.

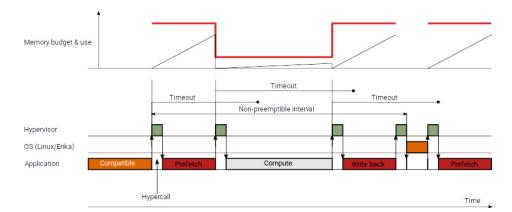

**Figure 2.5:** HERCULES Memory access scheduling & supervision. Source: [MSH17]

The system setup consists of a PREMized application which runs in userspace of Linux/Erika OS and Jailhouse hypervisor $[BBC^+17]$ . The whole execution process goes as follows[MSH17] (See Figure 2.5):

- 1. At the beginning of every non-preempted interval phase or compatible interval the application issues a hypercall.

- 2. When the hypervisor receives the call, it becomes aware of:

- a. the end of the previous phase

- b. the start of the current phase

- c. the memory and time budget that the current phase requests to have.

- 3. if the hypervisor detects the memory budget overrun during the application's execution, it signals about it and then acts as predefined in case of a critical fault.

Unfortunately, this solution has a drawback that affects the whole system performance. Experiments with that setup show (available here [Gai17]) that the hypercall lasts **21.72**  $\mu$ s in average and up to **58.42**  $\mu$ s in the worst case. That time could be improved with the use of some hardware instead of the hypervisor. Minimally, the watchdog functionality may be implemented in FPGA. Thus, the remainder of that thesis will discuss the ways how to achieve it.

# Chapter 3

# Hardware Platform Overview

This Chapter describes the capabilities of hardware given for the experiments with PREM. In attempts to mitigate the overhead mentioned at the end of Section 2.3, one should determine the right tools to achieve that, and this is the purpose of existence of this Chapter. In particular, the investigation here focuses on abilities of non-invasive tracing of DRAM access events for multiple CPU cores.

Section 3.1 presents the general overview of the given hardware. It also describes Trace subsystems available on the chip. Section 3.2 scopes out the ARM's CoreSight framework, its building blocks, and their roles. This section also provides a short overview of software tools available for working with that toolset. The last Section (3.3) describes ARM's Performance Monitoring Unit.

# **3.1** Zynq MPSoC's capabilities

The thesis specification suggests using Xilinx Zynq MPSoC Ultrascale+ platform for the PREM's experiments. It is reasonable proposition because the platform is cost-efficient, powerful, and it covers a broad range of applications. Moreover, Xilinx claims that Zynq MPSoC Ultrascale+ EG devices will find their use in Aerospace application and Zynq MPSoC Ultrascale+ EV are ideal for automotive tasks such as ADAS. In this work, however, the EG SoC is used, but the difference between them is only the fact that EV chips have an integrated H.264 / H.265 video codec.[bADASA]

#### **3.1.1** Zynq MPSoC Overview

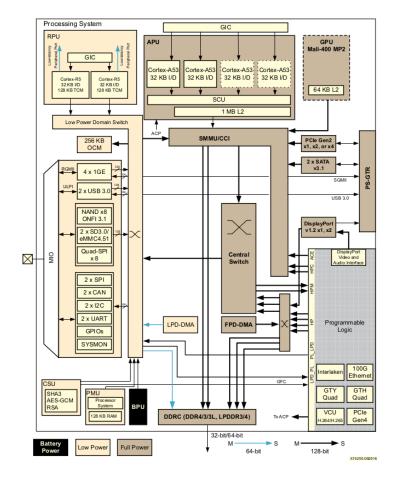

The top architecture overview of Zynq MPSoC Ultrascale+ is presented in Figure 3.1. That Figure shows all available processing units, I/O devices, platform controllers, etc. The points of interest, however, are Application Processing Unit (APU) and Programmable Logic (PL) and their interconnect with DRR4-type memory. APU consists of 64-bit Quad-core Cortex-A53 ARMv8 multiprocessing CPU, 1MB of L2 cache and Snooping Control Unit

(SPU) which cares about direct transfers between per-CPU L1 caches on purpose of maintaining cache coherence. The L2 cache is 16-way set-associative; Also, SPU supports Accelerator Coherency Port (ACP) port, which one could use to have I/O coherency of PL design, or even to have own L2 caches in PL coherent with the rest of the system (full-coherency mode). [Incc]

Figure 3.1: Zynq UltraScale+ MPSoC Top-Level Block Diagram. Source: [Incc]

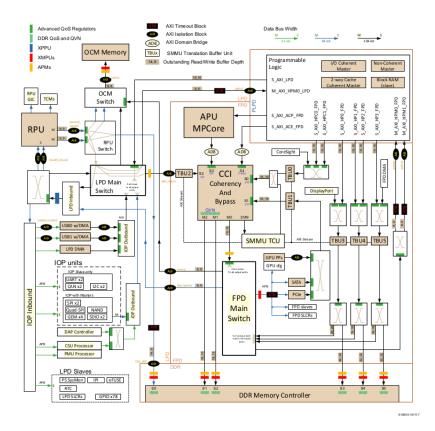

All components are interconnected with AMBA-compliant network through Advanced eXtensible Interfaces (AXI). This is a Network-On-Chip which consists of peer-to-peer connected devices in a master-slave manner; some of them are switches and bridges, which not only provide many-to-many connectivity but also synchronize signals coming from the different clock and power domains [Limf]. Figure 3.2 shows the interconnect in details.

Certain parts of the memory interconnect (especially the Cache Coherent Interconnect (CCI), DDR controller and QoS-400 Regulator) support Quality-of-Service (QoS) which could provide memory bandwidth throttling for the selected paths in the system. The master ports of these devices may be configured to give Low Latency (High Priority), High Throughput (Best

**Figure 3.2:** Zynq UltraScale+ MPSoC Top-Level AXI Interconnect Architecture. Source: [Incc]

Effort) or Isochronous access. This could be programmed either statically, or be controlled dynamically from PL.[Incc] The feature may be used to bound DRAM memory accesses in a manner of, e.g., MemGuard project ([YYP<sup>+</sup>13]), or in the collaboration of MemGuard and PREM where the throttling was applied on compatible phases of PREM model ([HSH17]).

PL could use several master and slave AXI ports to access the memory shared with Processing System (PS). The communication is also possible through multiplexed I/O interface (MIO) and extended multiplexed I/O interface (EMIO), PS-to-PL, and PL-to-PS interrupts.

#### **3.1.2** Tracing capabilities

Zynq Ultrascale+ provides wide abilities to trace the whole SoC. For example, integrated AXI Performance Monitors (APM) could monitor some of those connections. There are 4 APMs, and they could count the metrics at nine points of memory interconnect (See Figure 3.2). They could be used for the use-cases as obtaining latency metrics, read/write throughputs, count AXI bus events, debug AXI peripherals. (citation). APM is also available

3. Hardware Platform Overview

as an Intelectual Property (IP) block for FPGA to analyze an AXI traffic of implemented logic.[Inca]

There are three mods in which APM may operate. In the mode called **Advanced** APM can do *Event Logging*, where the specified events are stored in FIFO and then exported via AXI-Stream interface, and *Event Counting*, where the integrated metric counters are set on some event type. In **Profile Mode**, APM works similarly as in Advanced - Counting mode, but the metrics are predefined. The **Trace Mode** of APM shares the same idea as Profile Mode does: This is a simplified easy-to-use version of Advanced feature, in this case that is Event Logging. APM IP could emit an interrupt which may be set up on the overflow of metric counters or to signalize if the tracing FIFO is full.[Inca]

The important note about APM placed in SoC is "The PS-based APMs implement the advanced mode without error logging or the AXI Stream features."[Incc]

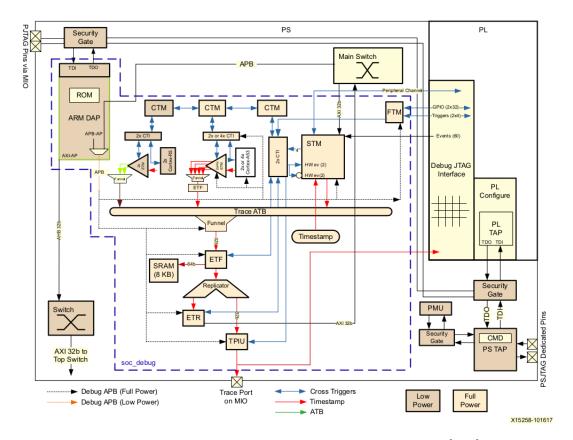

Xilinx also introduces the Fabric Trace Macrocell (FTM) (placed on the scheme in Figure 3.3) that allows cross-triggering between PS and PL. It has 32-bit GPIO from/to PL and four input/output trigger channels. The typical use-case of it is to start capturing in Integrated Logic Analyzer IP[Incb] placed in PL after some hardware event occurred at PS. The other option is to stimulate trace events with a trigger from PL. FTM is CoreSight-compliant device. For CoreSight description see the following Section 3.2.

### 3.2 ARM's CoreSight Framework

Zynq Ultrascale+ MPSoC platform implements the ARM CoreSight SOC-400 Trace & Debug components. This system provides an opportunity for non-invasive tracking of events coming from various devices on the chip. Figure 3.3 shows the complete layout of all CoreSight components available on Zynq Ultrascale+ MPSoC. This work heavily uses the features of Core-Sight to follow the memory access events due to non-intrusiveness of those tools and ability to export the needed information at runtime (See Chapter 4).

CoreSight devices are memory-mapped, and every such device must contain a set of specification-defined identification registers. It allows either software or hardware trace analyzer to detect the topology. A trace analyzer should know a physical address of CoreSight ROM table, where it should find the offsets of either devices or other ROM tables.[Lim13]

The trace data transfer consists of the following stages. *Trace units* (i. e. *trace sources*) emit a *trace packet* that contains trace unit's ID and encapsulated data. Then, the packet flows through *trace links* (which are connected by AMBA Advanced Trace Bus (ATB)) to *trace sinks*. The trace is then read

from the sink by trace analyzer and decoded.

Those software libraries and drivers may be useful when working with CoreSight:

- CoreSight Access Library (CSAL) [GCAL]

- Linux CoreSight driver already in kernel's mainline

- OpenCSD An OpenSource CoreSight Decoding library [GOAosCTD1]

CSAL provides C API for programming of almost all CoreSight components available on the market both from bare metal and Linux environment. This work uses that tool for CoreSight components configuration.

Linux CoreSight driver integrates the CoreSight system with standard performance evaluation tool - **perf**. Linaro's OpenCSD is able then to work together with perf to get a human-readable tracing of the kernel and user-space program execution.[GOAosCTD1]

Figure 3.3: Zynq UltraScale+ MPSoC Debug Block Diagram. Source: [Incc]

#### **3.2.1** Trace Sources

#### Embedded Trace Macrocell

Embedded Trace Macrocell (ETM) is a trace system element which targets on producing program traces. Those traces are generated at program's run-time. However, on purpose not to overload trace streams, ETM may be configured to notice only particular *trace elements* (i.e., events or event sequences). That filtering is highly customizable.

ETM is tightly coupled with CPU's core. Thus, every CPU core has a separate ETM. The hardware platform used in this work employs 4 Cortex-A53 cores and 2 Cortex-R5 cores (See overview in Figure 3.3), and R5's ETMs differ from the other ones in provided options. For instance, A53's ETMs do not support Data tracing. The remaining of the section focuses mainly on abilities of A53's ETM which implement the ETMv4 architecture.

Trace elements could be ([Incc]):

- Instruction address match

- Indirect branches and direct branches

- Instruction barrier instructions

- Exceptions

- Changes in processor instruction set state

- Changes in the processor security state

- Context-ID register changes

- Entering to debug state

- Cycle count during the traced parts

- Global system timestamps

- Target addresses for taken direct branches

- Trace control events such as:

Trace synchronization packets

Indicators of speculative execution for some instruction, if such event occurs

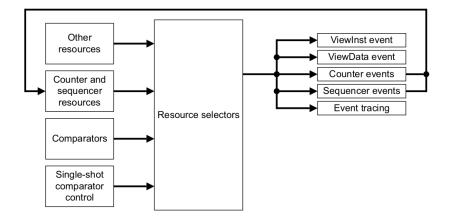

Those events are generated by so-called *trace resources*. They are configurable subsystems of ETM. Here is an overview of what resources Cortex-A53's ETM has. ([Limd],[Lime])

#### External inputs

These are input signals that other resources (Counters and resource selectors) may process to generate a trace event. Cortex-A53's ETM has 30 inputs: 4 Cross-Trigger inputs + 26 events from PMU. 4 of them can be selected.

#### External outputs

There are 4 of them. All are wired to Cross-Trigger interface. Any event from other resources may signal on an output; this is configured through Resource selectors (see below).

#### Address comparators

4 address comparators are available on Cortex-A53's ETM. They may be used to signal on a single preset address of the instruction which processor executed, or they may be used in pairs to create trace events when the address of the instruction is in (or out of) the preset range. The important notice here is that an address comparator also reacts on instructions executed speculatively.

Single-shot comparator

To mitigate the problem of noticing speculatively executed instructions in case of Address Comparator's use, the single-shot comparator is introduced. The examined ETM provides only one such trace resource. A Single-shot comparator chooses a single address or range address comparators to follow. When an instruction noticed by them is actually (non-speculatively) executed by a processor, the Signal-shot comparator fires. There is also a possibility to set that unit to reset after every fire so that it will be a "multiple-shot" one.

• Context identifier and Virtual context identifier comparators

They may be associated with Address comparators or used on its own. They react on a particular Context or Virtual Context IDs respectively.

Counters

Two decrementing counters are available. They may be used to count events on other resource units. A user may set initial and reset value for them, so every time a counter reaches zero it fires. The self-reload mode is also possible: counter resets with the provided value every time it reaches zero.

#### Sequencer

Provides a programmable 4-state machine to react on sertian sequence of events preprogrammed as state machine transitions.

• ViewInst unit provides the functionality of filtering of instruction trace events.

#### 3. Hardware Platform Overview

Resource selector units are used to interconnect the resources between each other. Figure 3.4 explains the concept. The example of resources configuration is provided in Chapter 4.

Figure 3.4: ETM's resource selection overview. Source: [Lime]

#### System Trace Macrocell

The System Trace Macrocell provides an opportunity to trace HW events, and a printf-style debug/trace option. On Zynq MPSoC, only PL events (60 of them) are connected to the HW event interface.[Incc]

Printf-style tracing means that STM can generate trace packets when software writes a message to STM registers. Combination of address and data in that message activate some "stimulus" port in STM, so STM bursts a packet associated with that port.

The example of STM use is presented in FreeRTOS board support package (see Listing 3.1). When the operating system enters in some function representing a system call (such as a task switch), the event's ID is written to STM's address. A developer could then analyze those events along with timestamps using a software (e.g., Xilinx SDK IDE, see screenshot in Figure 3.6 and the necessary setup option in Figure 3.5) that knows which trace IDs are defined for which syscalls. Some guides are provided at [UXSFAuS] • • • • • 3.2. ARM's CoreSight Framework

**Listing 3.1:** The parts of FreeRTOSSTMTrace.h which presents how FreeRTOS uses STM for tracing

```

#define STM_BASE

0xf8000000

#define FREERTOS_EMIT_EVENT(id)

Xil_Out8(STM_BASE +

(FREERTOS_STM_CHAN * 0x100), id)

#ifdef EXEC_MODE32

#define FREERTOS_EMIT_DATA(data) Xil_Out32((u32) (STM_BASE +

(FREERTOS_STM_CHAN * 0x100) + 0x18), (u32) data)

#else

#define FREERTOS_EMIT_DATA(data) Xil_Out64((u64) (STM_BASE +

(FREERTOS_STM_CHAN * 0x100) + 0x18), (u64) data)

#endif

. . .

#ifndef traceINCREASE_TICK_COUNT

/* Called before stepping the tick count after waking from

tickless idle sleep. */

#define traceINCREASE_TICK_COUNT( x ) {

\

FREERTOS_EMIT_EVENT(FREERTOS_INCREASE_TICK_COUNT);

١

FREERTOS_EMIT_DATA(x);

}

#endif

• • •

```

|                                                         |                                            | Board Supp | ort Package | Settings   | ×                                                          |

|---------------------------------------------------------|--------------------------------------------|------------|-------------|------------|------------------------------------------------------------|

| Board Support Package Set                               | ttings                                     |            |             |            |                                                            |

| Control various settings of your B                      | Board Support Package.                     |            |             |            |                                                            |

| <ul> <li>Overview</li> <li>freertos10_xilinx</li> </ul> | Configuration for OS: freertos10           | _xilinx    |             |            |                                                            |

| <ul> <li>drivers</li> </ul>                             | Name                                       | Value      | Default     | Туре       | Description                                                |

| psu_cortexa53_0                                         | stdin                                      | psu_uart_0 | none        | peripheral | stdin peripheral                                           |

|                                                         | stdout                                     | psu_uart_0 | none        | peripheral | stdout peripheral                                          |

|                                                         | <ul> <li>enable_stm_event_trace</li> </ul> | true       | false       | boolean    | Enable event tracing through System Trace Macrocell avai   |

|                                                         | enable_timer_tick_trace                    | true       | false       | boolean    | Enable tracing of timer tick events                        |

|                                                         | stm_channel                                | 0          | 0 0         | integer    | STM channel to use for trace. Valid channels are 0-65535   |

|                                                         | hook_functions                             | true       | true        | boolean    | Include or exclude application defined hook (callback) fun |

|                                                         | kernel_behavior                            | true       | true        | boolean    | Parameters relating to the kernel behavior                 |

|                                                         | kernel_features                            | true       | true        | boolean    | Include or exclude kernel features                         |

| ?                                                       |                                            |            |             |            | Cancel OK                                                  |

**Figure 3.5:** The necessary option setup in FreeRTOS BSP for enabling STM tracing in Xilinx SDK IDE.

3. Hardware Platform Overview

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | * = x 🕼 🗆 🗰 🗖 🖷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ©   • • 0 •   <i>*</i> •   • • | • 👳 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |                      |                                           | Quick Access                              |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------|-------------------------------------------|

| P STAP     PSU     PSU     PSU     PSU     PSU     POU (Reset)     PC Cortex-A53 #0     Cortex-A53 #1     Cortex-A53 #2 | Debug_freertos_demo_stm.elf on Loc<br>) (founning)<br>(fower On Reset)<br>(fower On Reset)<br>3 (fower On Reset)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | al (Local)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | % µ                                                                                                                                   | - <u>-</u>           |                                           | gis mixSCT mark Emul mai Modul 中<br>      |

| Reverta, L-Meix, workd.         I           Timestamp                                                                   | NucAky 22,06-347114 Take, Haya<br>Events type<br>cache<br>tad, Crasha Jar, voly, State<br>tad, Crasha<br>movel, Lais, Lar, voly, State<br>tada, Crasha<br>quine, create<br>quine, create<br>tad, create<br>movel, Stat, Create<br>movel, Stat, Create<br>tad, create<br>quine, create, failed<br>tad, create<br>tad, create<br>quine, create, failed<br>tad, create<br>quine, create, failed<br>tad, create<br>tad, | Contents<br>- Conten |                                | Freetros Analysis (F<br>Resources<br>• Run, May 22 00:54,<br>• Run May 22 00:54, | Nam_May-22_00-54/5TM_TP<br>Pointer<br>0x00000000001480<br>0x00000000001480<br>0x000000000001990<br>0x0000000000001990<br>0x0000000000 | 00:00:0              | 1 00:00:02                                | e l li l |

| Console 🕄 🧟 Tasks 🔲 St<br>Debug Virtual Terminal - Co                                                                   | DK Terminal 🎦 Problems 🕥 Executa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                | d 0 • d • -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                       | temory Trace Session | Manager 13<br>ertos_demo_stm.elf on Local | = °                                       |

Figure 3.6: FreeRTOS tracing in Xilinx SDK IDE.

#### **3.2.2** Trace Links and Sinks

#### Funnels & Replicators

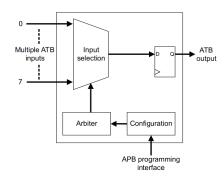

Replicators are non-programmable elements of the trace system which simply transfer the input trace on outputs. Funnels, however, are a little bit more sophisticated. They combine trace from multiple inputs into one output trace. One can configure input ports of a funnel to be enabled/disabled and to have a priority. The fixed priority scheme is then applied on inputs [Limc]. Block scheme of its principle is in Figure 3.7.

Figure 3.7: Funnel block diagram. Source: [Limc]

#### Trace Memory Controller

This CoreSight IP may present in one of three types:

- Embedded Trace Buffer (ETB) stores trace in a circular buffer on SRAM

- Embedded Trace FIFO (ETF) functions as a queue for trace packets for a reason of trace bandwidth normalization

- Embedded Trace Router (ETR) is a *trace sink* (endpoint of a trace bus). It sends trace packets to main memory through AXI.

Zynq MPSoC has 2 ETFs (8 KB) and 1 ETR. All these elements have programmable interfaces and are connected to CTI in purpose to start/stop trace or signal about buffer overflows etc.

#### Trace Port Interface Unit

This is also a final point of trace bus. It outputs trace data to an external device which decodes and stores/analyses the trace. Its outputs signals are TRACEDATA(32-bit width, could be reduced), TRACECTL (service signals), TRACECLK(250 MHz by default, may be provided externally). Before delivering the trace out, TPIU reformats it "re-associates trace sources' IDs with trace data"[Limc], to provide better bandwidth and an "ability for a trace decoder to resynchronize on frame boundary"[Limc]. To enable PL output (16-bit width data at MIO and 32-bit data at EMIO ports): "The TPIU.EXTCTL\_OUT\_Port register must be set to output trace into the PL."[Incc]

#### 3.2.3 Embedded Cross-Trigger

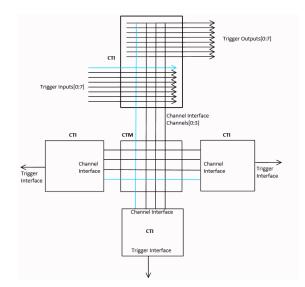

**Figure 3.8:** ECT block diagram. "The CTI at the top is configured to propagate the trigger event on Trigger Input 0 to Channel 0." Source: [UXSCT]

The Embedded Cross-Trigger (ECT) system distributes trigger signals between all trace and debug elements. Two main elements are presented here: Cross-Trigger Interface (CTI) and Cross-Trigger Matrix (CTM).

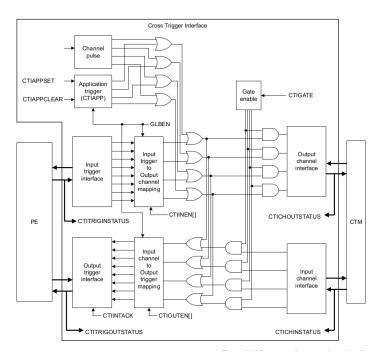

CTI is in charge of mapping signals between input/output ports and input/output channels. The mapping is configured through CTI's registers (internal logic is presented in Figure 3.9). To propagate the signal from internal channel outside, CTIGATE register bits should be set. There is also an opportunity to set some channels active from software, or, to send a trigger (channel pulse) through CTIAPPSET/CTIAPPCLEAR, which is sometimes helpful for debug purposes. Every Zynq MPSoC's CTI has 8 input and 8 output trigger signals (but some are reserved).

CTM broadcasts signals to other CTIs. The channels coming from CTI are combined in OR manner. Figure 3.8 illustrates the example of trigger propagation. Zynq MPSoC's CTMs have 4 channels.

Figure 3.9: CTI internal logic overview. Source: [Lima]

Channel interface consists of two pairs of input and output wires (CHIN/-CHOUT, CHINACK/CHOUTACK) when acknowledge is asynchronous, and contains additional wire CHCLK when the interface implemented as synchronous. An "asynchronous interface uses a basic 4-phase handshaking protocol" [Limb].

There are 8 CTIs on Zynq MPSoC: 2 are for cores of RPU unit, other 4 are connected to Cortex-A53 cores (each on its own core), and the last 2

are for the whole SoC. Every Cortex A53 CTI accepts signals from ETMs (External outputs), PMU (PMUIRQ), and the debug request from CPU. For out triggers, it has the ETM's external inputs wired, may send an interrupt, and debug halt command to CPU. The next CTI, SoC's one, handles FTM and STM triggers (in and out). The other SoC's CTI triggers ETFs and TPIU. More precise information on ECT wiring for Zynq MPSoC is provided here - [UXSCTiZUM].

### **3.3** ARM's Performance Monitoring Unit

Performance monitoring unit enables a user to count selected processor events such as memory bus accesses, cache accesses, exceptions and so on. Every core of APU has its own PMU so that one could have information about such events per every core separately. It is useful especially in case of trying to implement per-processor memory access monitoring.

PMU available at Cortex A53 has one 64-bit wide clock counter, which is often used for measuring the execution time of a program part, and six event counters (32-bit wide). Event counters may be configured on a specific event type (the full list is available). The counters count up and could be set to emit an interrupt (PMUIRQ) on overflow, meaning – when the counter becomes equal to zero.

22 events from PMU are wired to ETM's external inputs so that the ETM may use these as trace events. This facility is used in this work as described in Chapter 4.

# Chapter 4 PREM Watchdog Implementation

### 4.1 Concept

The aim of creating the PL Watchdog system is to non-invasively monitor the number of memory accesses made by APU cores per every PREM phase execution. The two possible on-chip hardware provide such functionality: APM (See Section 3.1.2) and PMU (See Section 3.3). APM, however, does not fit as a tool because of its inability to differentiate the initiators of a memory request. It can measure the overall traffic, e.g., for read/write byte count coming from CCI master, but it has no tracing points which are closer to cores than that.

From the variety of memory access events that PMU provides (cite armv8), L2\_CACHE\_REFILL was chosen to be followed. L2\_CACHE\_REFILL defined as "Each read from or write to the cache that causes a refill from outside the Level 1 and Level 2 caches" [Lima], what is a result of the L2 cache miss. In PREM, it is essential to reduce cache misses on a shared resource to a minimum, because it influences other users (CPU) of that shared resource. So the mentioned memory budget for PREM phase may be represented as the number of permitted cache misses.

The next problem to solve is how to deliver the event from PMU to PL. The investigation done in Section 3.3 narrows the following possibilities:

- 1. Software or hardware could directly read the event counter value. This option does not fit due to the possible influence on the system being watched.

- 2. Catch PMUIRQ routed through the Generic Interrupt Controller to the PL. A breaking of the rule of non-invasiveness is also possible here.

- 3. The other option is to route PMUIRQ using core's CTI directly into PL. Even though the PL has an interface to deliver the CTIINT signal directly, writing to CTIACK (check the name) register should be done

to acknowledge it. A trigger would not fall without the acknowledgment so that the next event will be missed.

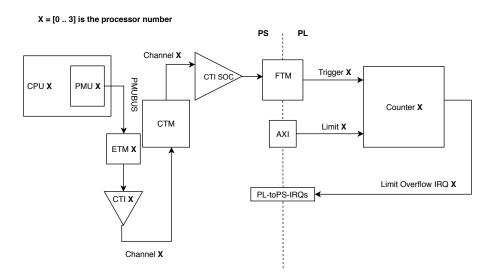

4. Use ETM to react on the preset PMU event and then propagate it through ECT all the way up to FTM's interface. Refer to the CoreSight System overview in Figure 3.3.

Also, the watchdog logic should be aware of a memory limit for the currently monitored PREM phase. The only possibility to send the limit value to the PL is to use AXI memory interconnect, so the PL logic will appear as a memory mapped device. This information may then be delivered with a PREMized program, i.e., instructions that will write that value into PL's memory are called at the beginning of every PREM interval.

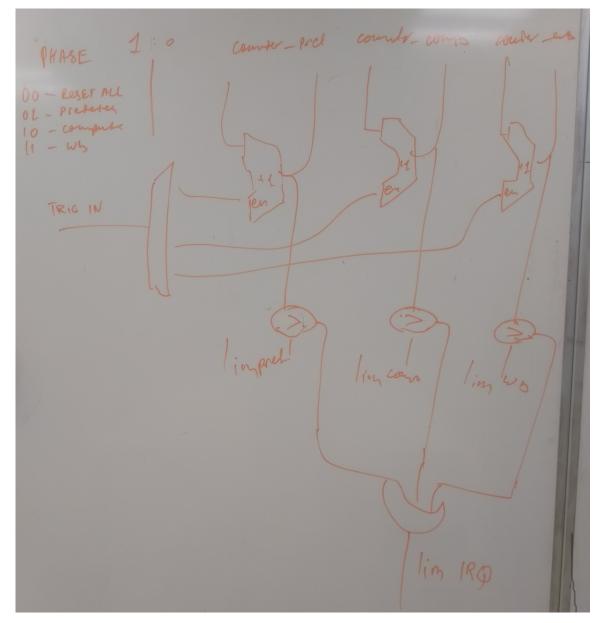

The Figure 4.1 provides an overview of the final concept. The Figure 4.1 illustrates that every APU's core has its Counter in PL (**X** denotes the CPU ID: e.g., the CPU**3** is connected to ETM**3**, and CTI**3** is connected to CTM at the **third** channel and so on). Counter X counts and acknowledges triggers through FTM's Trigger interface. Counter **X** is an AXI slave, so the message about Limit for processor **X** is delivered from SW through memory mapped interface. Finally, every Counter sends an interrupt through the provided PL to PS interrupt delivery interface in case of the given limit is overflown.

Figure 4.1: The implementation concept overview.

# 4.2 CoreSight System Configuration

To configure all the CoreSight devices mentioned in Section 4.1, CSAL is used. It adds some abstraction above the memory mapped registers to make the programmer's work easier. Moreover, the support of both Linux and bare metal environment makes the configuration code portable.

The CSAL workflow starts with calling cs\_init() function which initializes internals of the framework. Then, a device should be registered using the cs\_device\_register(cs\_phys\_addr\_t addr), where physical device address must be provided as an argument. That function unlocks the device and saves a handle into library's internal structure. CoreSight device unlocking must involve several writes to ARM's registers; the exact algorithm is provided here [Limb]; without the unlocking, the device does not accept writes.

The following sections describe the configuration of single CoreSight blocks to make the modeled concept work.

#### PMU

The only configuration which every PMU must have is calling cs\_pmu\_bus\_export() function. This sets the fifth bit in PMCR register of PMU to allow the event export to ETM.

#### ETM

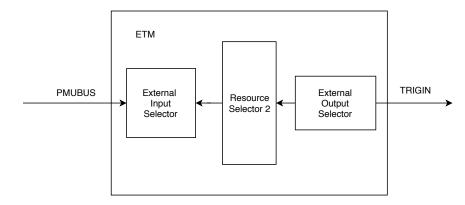

The diagram showing the combination of ETM's resources used is provided in Figure 4.2. Firstly, ETM device must be cleared from any previous settings by calling cs\_etm\_clean(). Then, the new configuration structure (cs\_etmv4\_config\_t) is created, which consists of register values that soon will be set on ETM. Those registers are configured as follows (refer to ETM register description in [cite]):

- 1. External Input Select Register bits [4:0] are set with L2D\_CACHE\_REFILL event number + 4 because the first four event numbers mean ETM input triggers. This opens external input 0.

- 2. Resource Selector 2 Register (may be any from 2nd to 8th because the first two are reserved for other use) is set with the number of external input (0) and the type of resource to select (external input group is set to 0). This selects the External Input 0.

- 3. Then, one must configure the Event Control 0 Register to connect Resource Selector 2 with External Output 0. Bits [3:0] are set with Resource Selector number.

After all the configuration is done, it must be written to ETM by calling cs\_etm\_config\_put(), and ETM must be enabled with cs\_etm\_disable\_programming().

4. PREM Watchdog Implementation

Figure 4.2: ETM's configuration.

#### ECT configuration

Near-to-CPU CTI is configured to send a signal from Trigger input 4 (which comes from ETM) to channel **X**, where **X** denotes the number of CPU. Thus, every CPU occupies its own channel in CTM matrix. The CTI which is connected to FTM maps channels 0-3 to trigger outputs 0-3 which are connected to FTM. And, FTM does not require any configuration.

### 4.3 Programmable Logic Design